# A Complete Guide by Günther Daubach

2<sup>ND</sup> EDITION

### WARRANTY

Parallax Inc. warrants its products against defects in materials and workmanship for a period of 90 days from receipt of product. If you discover a defect, Parallax Inc. will, at its option, repair or replace the merchandise, or refund the purchase price. Before returning the product to Parallax, call for a Return Merchandise Authorization (RMA) number. Write the RMA number on the outside of the box used to return the merchandise to Parallax. Please enclose the following along with the returned merchandise: your name, telephone number, shipping address, and a description of the problem. Parallax will return your product or its replacement using the same shipping method used to ship the product to Parallax.

## 14-DAY MONEY BACK GUARANTEE

If, within 14 days of having received your product, you find that it does not suit your needs, you may return it for a full refund. Parallax Inc. will refund the purchase price of the product, excluding shipping/handling costs. This guarantee is void if the product has been altered or damaged. See the Warranty section above for instructions on returning a product to Parallax.

## COPYRIGHTS AND TRADEMARKS

This documentation is copyright 2004 by Parallax Inc. By downloading or obtaining a printed copy of this documentation or software you agree that it is to be used exclusively with Parallax products. Any other uses are not permitted and may represent a violation of Parallax copyrights, legally punishable according to Federal copyright or intellectual property laws. Any duplication of this documentation for commercial uses is expressly prohibited by Parallax Inc.

BASIC Stamp, Stamps in Class, Board of Education, Boe-Bot, SumoBot, Toddler, and SX-Key are registered trademarks of Parallax, Inc. HomeWork Board, Parallax, and the Parallax logo are trademarks of Parallax Inc. If you decide to use registered trademarks of Parallax Inc. on your web page or in printed material, you must state that "(trademark) is a (registered) trademark of Parallax Inc." upon the first appearance of the trademark name in each printed document or web page. Other brand and product names are trademarks or registered trademarks of their respective holders.

#### ISBN 1-928982-16-6

2007 Aug. 2nd Ed. 2nd Pr.

#### DISCLAIMER OF LIABILITY

Parallax Inc. and Guntheer Daubach are not responsible for special, incidental, or consequential damages resulting from any breach of warranty, or under any legal theory, including lost profits, downtime, goodwill, damage to or replacement of equipment or property, or any costs of recovering, reprogramming, or reproducing any data stored in or used with Parallax products. Parallax Inc. is also not responsible for any personal damage, including that to life and health, resulting from use of any of our products. You take full responsibility for your SX microcontroller application, no matter how lifethreatening it may be.

#### TECHNICAL SUPPORT AND INTERNET RESOURCES

We offer a variety of internet resources and avenues for receiving technical support:

E-mail: support@parallax.com Web: www.parallax.com/sx Phone: 916.624.8333 Toll-free: 888.99.STAMP (Continental U.S. only) Forums: forums.parallax.com/forums

Our moderated forums include one specifically for people interested in programming the SX microcontroller with Parallax assembly language SX-Key tools, and third-party SX/B (BASIC) and C compilers.

### ERRATA

While great effort is made to assure the accuracy of our texts, erros may still exist. If you find an error, please send an email to editor@parallax.com. If an errata sheet is necessary, it will be posted to this book's product page (product #70002) at www.parallax.com.

## **Table of Contents**

| 1                                                                                                                                         | Section I - Tutorial                                                                                                              | 3                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                       | Introduction                                                                                                                      | 3                                                                                                              |

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3                                                                                                            | SX Development - What You Need<br>The Tools<br>Prototyping Systems<br>A "Home-brew" Prototyping System                            | 5<br>5                                                                                                         |

| 1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.4.1<br>1.3.4.2<br>1.3.4.3<br>1.3.5<br>1.3.6<br>1.3.7<br>1.3.8<br>1.3.9<br>1.3.10<br>1.3.11 | SX-Key Quick Start using the Parallax SX-Key                                                                                      | 8         9         15         15         15         16         17         20         21         23         26 |

| 1.4<br>1.4.1<br>1.4.2<br>1.4.3                                                                                                            | SX Configuration - ORG/DS - Conditional Branches<br>Configuration Directives<br>The ORG and DS Directives<br>Conditional Branches | 28<br>28<br>29                                                                                                 |

| $1.5 \\ 1.5.1 \\ 1.5.2 \\ 1.5.3 \\ 1.5.4 \\ 1.5.5 \\ 1.5.6 \\ 1.5.6.1$                                                                    | Subroutines - Symbols - Data Memory                                                                                               | 33         34         36         38         41         45         45                                           |

| 1.5.6.2<br>1.5.7                                                                                                                          | SX 48/52<br>Symbolic Variable Names                                                                                               | 52                                                                                                             |

|                                                                                                                                           | -                                                                                                                                 |                                                                                                                |

| 1.5.8   | The EQU, SET and = Directives                   | 53  |

|---------|-------------------------------------------------|-----|

| 1.5.9   | Some Thoughts about Data Memory Usage           |     |

| 1.5.10  | Don't Forget to Select the Right Bank           |     |

| 1.5.11  | Saving the Current Bank in a Subroutine         |     |

| 1.5.12  | Routines for an FSR Stack                       |     |

| 1.5.13  | The "#"-Pitfall                                 |     |

| 1.6     | Arithmetic and Logical Instructions             | 67  |

| 1.6.1   | Arithmetic Instructions                         |     |

| 1.6.1.1 | Addition                                        | 67  |

| 1.6.1.2 | Skip Instructions                               |     |

| 1.6.1.3 | The TEST Instruction                            |     |

| 1.6.1.4 | Multi-Byte-Addition                             |     |

| 1.6.1.5 | Subtraction                                     |     |

| 1.6.1.6 | Signed Numbers                                  |     |

| 1.6.2   | Incrementing and Decrementing                   | 73  |

| 1.6.3   | Arithmetic Instructions and Multi-Byte Counters |     |

| 1.6.4   | The DEVICE CARRYX Directive                     |     |

| 1.6.5   | Logical Operations                              | 76  |

| 1.6.5.1 | AND                                             |     |

| 1.6.5.2 | OR                                              |     |

| 1.6.5.3 | XOR                                             | 79  |

| 1.6.5.4 | NOT                                             | 80  |

| 1.6.6   | Rotate instructions                             | 80  |

| 1.6.6.1 | Multiplication and Division                     |     |

| 1.6.7   | The SWAP Instruction                            |     |

| 1.6.8   | The DC (Digit Carry) Flag                       |     |

| 1.6.9   | MOV Instructions with Arithmetic Functions      |     |

| 1.7     | MOV Instructions                                | 90  |

| 1.7.1   | Basic MOV Instructions                          | 90  |

| 1.7.2   | Compound MOV Instructions                       | 91  |

| 1.8     | Recognizing Port Signals                        | 94  |

| 1.8.1   | Recognizing Signal Edges at Port B              |     |

| 1.8.1.1 | MODE and Port Configuration Registers           |     |

| 1.8.1.2 | Signal Edges at Port B                          |     |

| 1.8.1.3 | De-bouncing Mechanical Contacts                 |     |

| 1.9     | Interrupts - The OPTION Register                | 102 |

| 1.9.1   | Interrupts                                      |     |

| 1.9.1.1 | Asynchronous Interrupts                         |     |

|         |                                                 |     |

| 1.9.1.2  | Synchronous (Timer-Controlled) Interrupts             | 110 |

|----------|-------------------------------------------------------|-----|

| 1.9.1.3  | The Prescaler                                         |     |

| 1.9.1.4  | Interrupts Caused by Counter Overflows                |     |

| 1.9.2    | The OPTION Register Bits and their Meaning            | 120 |

| 1.10     | The Watchdog - Reset Reasons - Conditional Assembly   | 121 |

| 1.10.1   | The Watchdog Timer                                    | 121 |

| 1.10.2   | Determining Reset Reasons                             | 124 |

| 1.10.3   | Conditional Assembly                                  | 125 |

| 1.10.3.1 | More Directives for Conditional Assembly              | 126 |

| 1.10.4   | "To Watchdog or not to Watchdog"                      | 128 |

| 1.11     | The Sleep Mode and Wake-up                            |     |

| 1.11.1   | Wake-ups Caused by Port B Signal Edges                | 129 |

| 1.11.2   | Using the Watchdog Timer for Wake-ups                 | 133 |

| 1.12     | Macros - Expressions - Symbols - Device Configuration |     |

| 1.12.1   | Macro Definitions                                     |     |

| 1.12.1.1 | Macros or Subroutines?                                |     |

| 1.12.2   | Expressions                                           |     |

| 1.12.3   | Data Types                                            |     |

| 1.12.4   | Symbolic Constants                                    | 141 |

| 1.12.5   | The DEVICE Directives                                 | 144 |

| 1.12.6   | The FREQ Directive (SX-Key only)                      |     |

| 1.12.7   | The ID Directive                                      |     |

| 1.12.8   | The BREAK Directive (SX-Key only)                     |     |

| 1.12.9   | The ERROR Directive                                   |     |

| 1.12.10  | The END Directive                                     |     |

| 1.13     | The Analog Comparator                                 | 148 |

| 1.13.1   | The Comparator and Interrupts                         | 150 |

| 1.13.2   | The Comparator and the Sleep Mode                     | 151 |

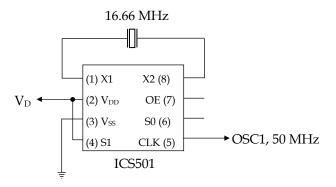

| 1.14     | System Clock Generation                               | 152 |

| 1.14.1   | The Internal Clock Generator                          |     |

| 1.14.2   | Internal Clock Generator with External R-C Network    | 153 |

| 1.14.3   | External Crystal/Ceramic Resonator                    | 153 |

| 1.14.4   | External Clock Signals                                |     |

| 1.14.5   | External Clock Signal using a PLL                     |     |

| 1.14.6   | Selecting the Appropriate Clock Frequency             |     |

| 1.15     | The Program Memory                                    | 157 |

|          |                                                       |     |

| 1.15.1   | Organizing the Program Memory                      | 157  |

|----------|----------------------------------------------------|------|

| 1.15.1.1 | The PAGE Instruction                               | 158  |

| 1.15.1.2 | The @jmp and @call Options                         |      |

| 1.15.1.3 | Subroutine Calls across Memory Pages               | 161  |

| 1.15.2   | How to Organize Program Memory                     |      |

| 1.16     | Tables - RETIW and IREAD                           | 164  |

| 1.16.1   | Tables                                             | 164  |

| 1.16.1.1 | The RETW Instruction                               | 164  |

| 1.16.1.2 | Reading Program Memory Using the IREAD Instruction | 169  |

| 1.17     | More SX Instructions                               | 172  |

| 1.17.1   | Compare Instructions                               | 172  |

| 1.17.1.1 | CJA (Compare and Jump if Above)                    |      |

| 1.17.1.2 | CJAE (Compare and Jump if Above or Equal)          | 172  |

| 1.17.1.3 |                                                    | 1 70 |

| 1.17.1.4 | CJBE (Compare and Jump if Below or Equal)          | 173  |

| 1.17.1.5 | CJE (Compare and Jump if Equal)                    | 173  |

| 1.17.1.6 |                                                    |      |

| 1.17.2   | Decrement/Increment with Jump                      | 174  |

| 1.17.2.1 | DJNZ (Decrement and Jump if Not Zero)              | 174  |

| 1.17.2.2 | IJNZ (Increment and Jump if Not Zero)              | 174  |

| 1.17.3   | Conditional Jumps                                  | 174  |

| 1.17.3.1 | JNB (Jump if Not Bit set)                          | 174  |

| 1.17.3.2 | JNC (Jump if Not Carry set)                        | 175  |

| 1.17.3.3 | JNZ (Jump if Not Zero)                             | 175  |

| 1.17.4   | Conditional Skips                                  | 175  |

| 1.17.4.1 | CSA (Compare and Skip if Above)                    | 175  |

| 1.17.4.2 | CSAE (Compare and Skip if Above or Equal)          | 175  |

| 1.17.4.3 | CSB (Compare and Skip if Below)                    | 176  |

| 1.17.4.4 | CSBE (Compare and Skip if Below or Equal)          |      |

| 1.17.4.5 | CSE (Compare and Skip if Equal)                    | 176  |

| 1.17.4.6 | CSNE (Compare and Skip if Not Equal)               | 176  |

| 1.17.5   | MOV and Conditional Skip                           | 177  |

| 1.17.5.1 | MOVSZ (MOVe and Skip if Zero)                      |      |

| 1.17.6   | NOP (No OPeration)                                 | 177  |

| 1.17.7   | SKIP                                               | 177  |

| 1.18     | Virtual Peripherals                                | 179  |

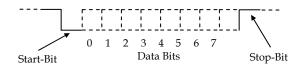

| 1.18.1   | The Software UART, a VP Example                    | 179  |

| 1.18.1.1 | The Transmitter                                    | 185  |

|          |                                                    |      |

| 1.18.1.2 | The Receiver                                             | 187 |

|----------|----------------------------------------------------------|-----|

| 1.18.1.3 | Utility Routines                                         | 189 |

| 1.18.1.4 | The Main Program                                         | 191 |

| 1.18.1.5 | Handshaking                                              | 192 |

| 1.18.2   | Conclusion                                               | 193 |

| 2        | Section II - Reference                                   | 197 |

| 2.1      | Introduction                                             | 197 |

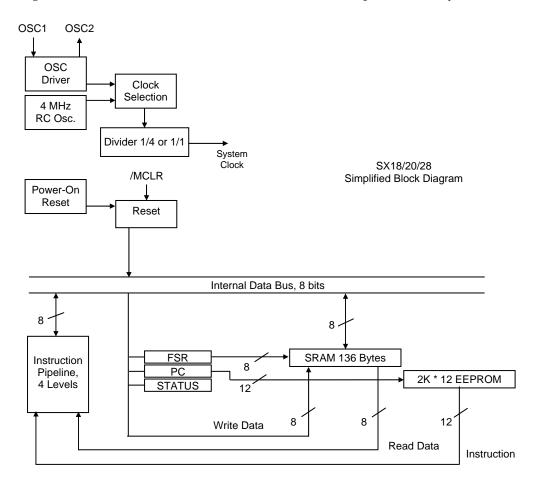

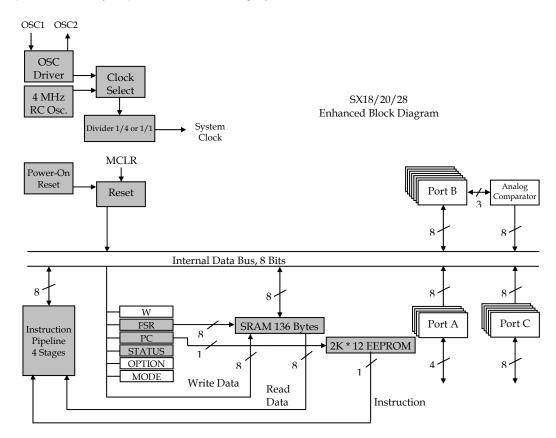

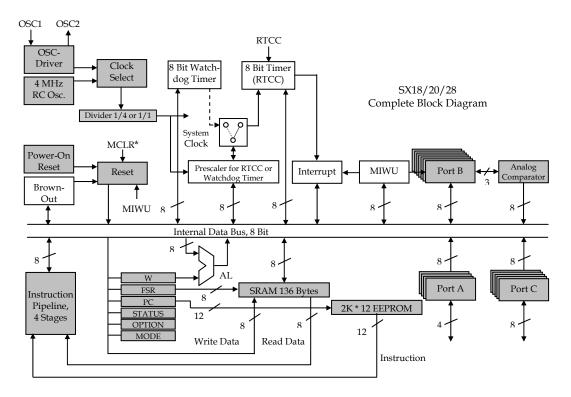

| 2.2      | The SX internals (simplified)                            | 199 |

| 2.2.1    | How SX Instructions are Constructed                      | 202 |

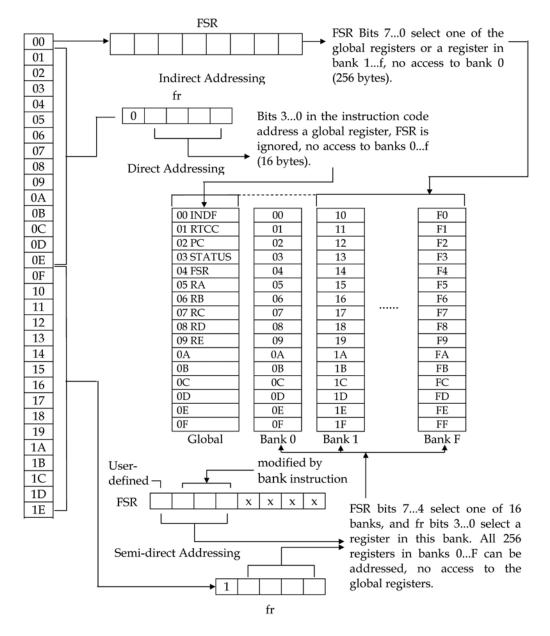

| 2.2.2    | Organization of the Data Memory and how to Address it    |     |

| 2.2.2.1  | SX 18/20/28                                              | 203 |

| 2.2.2.2  | SX 48/52                                                 | 205 |

| 2.2.3    | Organization of Program Memory and how to Access it      | 207 |

| 2.2.4    | The SX Special Registers and the I/O Ports               |     |

| 2.2.4.1  | The W Register                                           | 209 |

| 2.2.4.2  | The I/O Registers (Ports)                                | 210 |

| 2.2.4.3  | Read-Modify-Write Instructions                           |     |

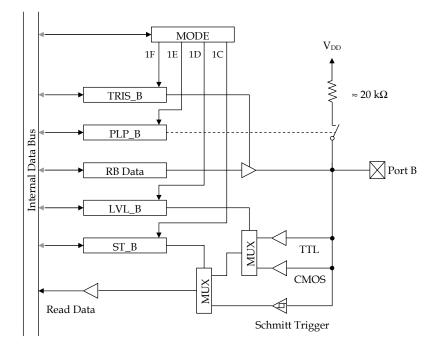

| 2.2.4.4  | Port Block Diagram                                       |     |

| 2.2.4.5  | The Data Direction Registers                             |     |

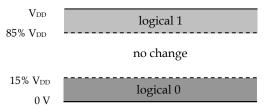

| 2.2.4.6  | The Level Register                                       |     |

| 2.2.4.7  | Pull-up Enable Registers                                 |     |

| 2.2.4.8  | The Schmitt Trigger Enable Registers                     |     |

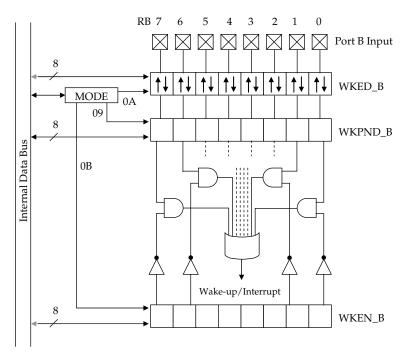

| 2.2.4.9  | The Port B Wake Up Configuration Registers               |     |

| 2.2.4.10 | The Port B Analog Comparator                             | 217 |

| 2.2.4.11 | More Configuration Registers (SX 48/52)                  | 217 |

| 2.2.4.12 | Addressing the I/O Configuration Registers (SX 18/20/28) | 218 |

| 2.2.4.13 | Addressing the SX 48/52 I/O Configuration Registers      |     |

| 2.2.5    | Interrupts, Watchdog and Brown-Out                       |     |

| 2.2.5.1  | Interrupts                                               | 222 |

| 2.2.5.2  | The Watchdog Timer                                       | 225 |

| 2.2.5.3  | Additional Bits in the OPTION Register                   |     |

| 2.2.5.4  | Monitoring V <sub>DD</sub> - The Brown-Out Detection     | 227 |

| 2.2.5.5  | Determining the Reason for a Reset                       |     |

| 2.2.6    | The Stack Memory                                         | 229 |

| 2.2.7    | The FUSE Registers                                       |     |

| 2.2.7.1  | The FUSE Registers (SX18/20/28)                          |     |

| 2.2.7.2  | The Fuse Registers (SX 48/52)                            |     |

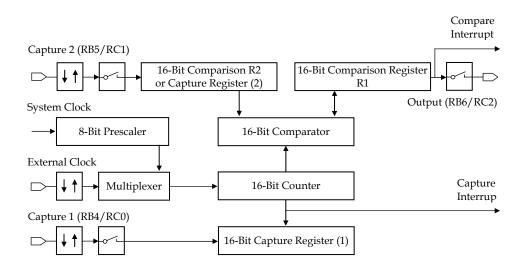

| 2.2.8    | The SX 48/52 Multi-Function Timers                       |     |

|          |                                                          |     |

| 2.2.8.1<br>2.2.8.2 | PWM Mode                                       | 238<br>238 |

|--------------------|------------------------------------------------|------------|

| 2.2.8.3            | Software Timer Mode                            |            |

| 2.2.8.4            | External Event Counter<br>Capture/Compare Mode | 239        |

| 2.2.8.5            | The SX48/52 Timer Control Registers            |            |

| 3                  | Section III – Quick Reference                  | 247        |

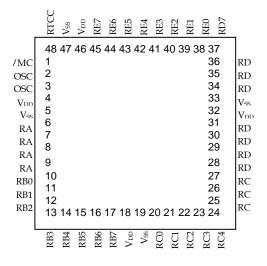

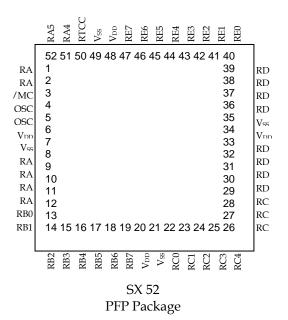

| 3.1                | SX Pin Assignments                             | 247        |

| 3.2                | Commonly used Abbreviations                    | 249        |

| 3.3                | Instruction Overview                           | 252        |

| 3.3.1              | Comments on the Instruction Overview Tables    | 252        |

| 3.3.2              | Instructions in Alphabetic Order               | 253        |

| 3.3.3              | Instructions by Functions                      |            |

| 3.4                | Special Registers                              | 260        |

| 3.4.1              | Option                                         | 260        |

| 3.4.2              | Status                                         | 260        |

| 3.4.3              | FSR                                            | 261        |

| 3.5                | Addressing the Port Control Registers          | 261        |

| 3.5.1              | SX 18/20/28                                    |            |

| 3.5.2              | SX 48/52                                       |            |

| 3.6                | Port Control Registers                         | 264        |

| 3.6.1              | TRIS (Direction)                               |            |

| 3.6.2              | LVL (Level Configuration)                      | 264        |

| 3.6.3              | PLP (Pull-up Configuration)                    | 265        |

| 3.6.4              | ST (Schmitt Trigger Configuration)             | 265        |

| 3.6.5              | WKEN_B (Wake Up Enable)                        |            |

| 3.6.6              | WKED_B (Wake Up Edge Configuration)            |            |

| 3.6.7              | WKPND_B (Wake Up Pending Flags)                |            |

| 3.6.8              | CMP_B (Comparator)                             | 266        |

| 3.6.9              | T1CNTA (Timer 1 Control A) (SX 48/52 only)     |            |

| 3.6.10             | T1CNTB (Timer 1 Control B) (SX 48/52 only)     |            |

| 3.6.11             | T2CNTA (Timer 2 Control A) (SX 48/52 only)     |            |

| 3.6.12             | T2CNTB (Timer 2 Control B) (SX 48/52 only)     | 268        |

| 4                  | Section IV - Applications                      | 271        |

| 4.1                | Function Generators with the SX                | 271        |

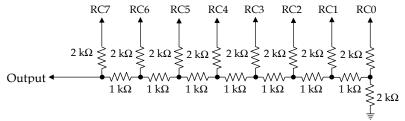

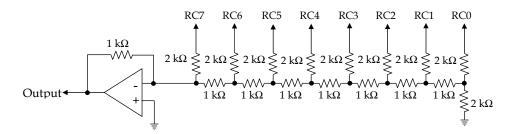

| 4.1.1              | A Simple Digital-Analog Converter              | 272        |

| 4.1.2              | A Ramp Generator                                                                        | 273 |

|--------------------|-----------------------------------------------------------------------------------------|-----|

| 4.1.2.1            | A Ramp Generator With a Pre-defined Frequency                                           |     |

| 4.1.3              | Generating a Triangular Waveform                                                        |     |

| 4.1.4              | Generating Non-linear Waveforms                                                         |     |

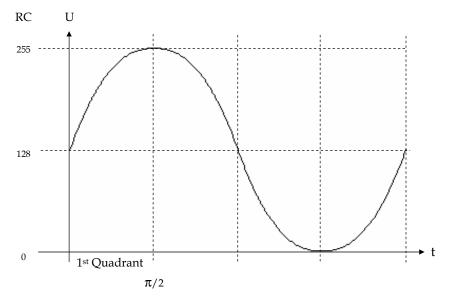

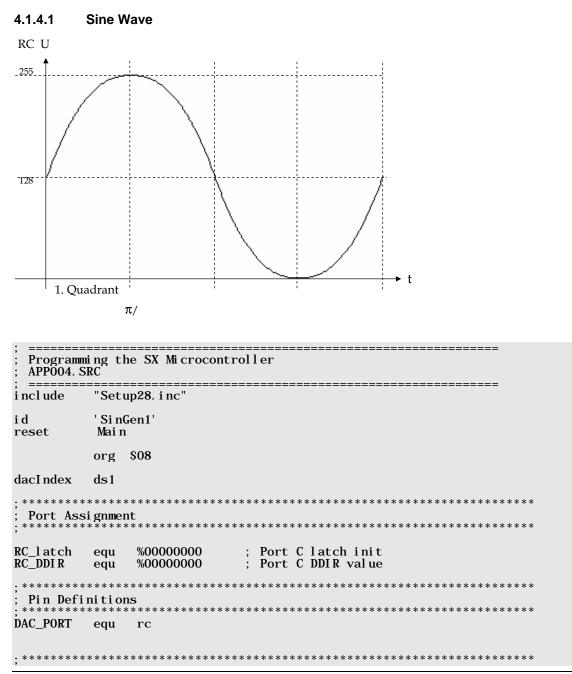

| 4.1.4.1            | Sine Wave                                                                               | 280 |

| 4.1.4.2            | Sine Generator with a Defined Frequency                                                 |     |

| 4.1.4.3<br>4.1.4.4 | Superimposed Sine-Waves<br>Generating a Sine Wave from a 1 <sup>st</sup> Quadrant Table |     |

| 4.1.4.4            | Generating Other Waveforms                                                              |     |

|                    |                                                                                         |     |

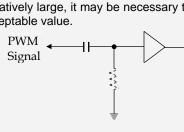

| 4.2                | Pulse Width Modulation (PWM) with the SX Controller                                     |     |

| 4.2.1              | Simple PWM VP                                                                           | 288 |

| 4.2.2<br>4.2.3     | PWM VP with constant Period                                                             | 290 |

| 4.2.3              | More Areas Where PWM is Useful                                                          | 292 |

| 4.3                | Analog-Digital Conversion with the SX                                                   |     |

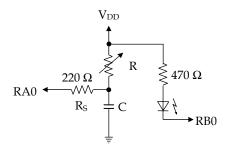

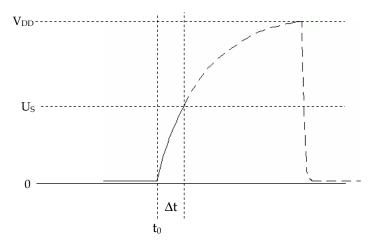

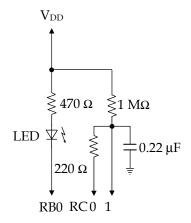

| 4.3.1              | Reading a Potentiometer Setting                                                         | 293 |

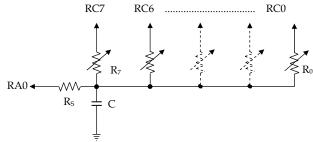

| 4.3.1.1            | Reading more Potentiometer Settings                                                     |     |

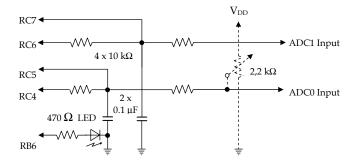

| 4.3.2              | A/D Converter Using Bitstream Continuous Calibration                                    | 301 |

| 4.4                | Timers as Virtual Peripherals                                                           | 307 |

| 4.4.1              | A Clock Timer – an Example                                                              |     |

| 4.4.2              | General Timer VPs und Timed Actions                                                     | 311 |

| 4.4.2.1            | Execution within the ISR                                                                |     |

| 4.4.2.2            | Testing the Timers in the Mainline Program                                              | 311 |

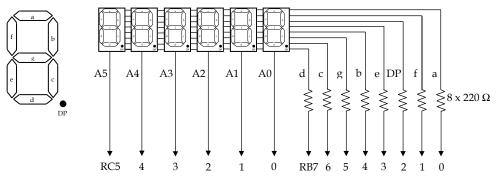

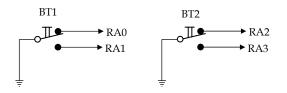

| 4.5                | Controlling 7-Segment LED Displays                                                      | 314 |

| 4.5.1              | Program Variations                                                                      |     |

| 4.6                | An SX Stopwatch                                                                         |     |

| 4.7                | A Digital SX Alarm Clock                                                                | 338 |

| 4.7.1              | When the Clock is Wrong                                                                 |     |

|                    |                                                                                         |     |

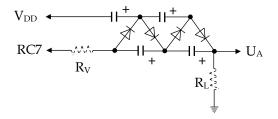

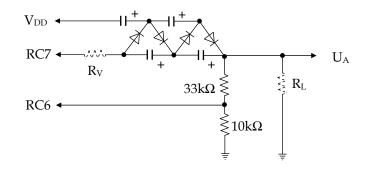

| 4.8                | Voltage Converters                                                                      | 357 |

| 4.8.1              | A Simple Voltage Converter                                                              | 357 |

| 4.8.2              | A Regulated Voltage Converter                                                           | 358 |

| 4.9                | Testing Port Outputs                                                                    | 361 |

| 4.10               | Reading Keyboards                                                                       | 364 |

| 4.10.1             | Scanning a Key Matrix, First Version                                                    |     |

| 4.10.1.1           | Decoding the Key Number                                                                 | 370 |

| 4.10.1.2           | Initial "Quick Scan"                                                                    | 371 |

|                    |                                                                                         |     |

| 4.10.3       Need more Port Pins for the Keyboard Matrix?       378         4.11       An "Artificial" Schmitt Trigger Input       380         4.12       A Software FIFO       382         4.13       PC Routines       388         4.13.1       The PC Bus       388         4.13.2       The Basic PC Protocol       389         4.13.2.1       "Master" and "Slave"       389         4.13.2.2       The Basic PC Protocol       389         4.13.2.3       Data Transfer, and Clock Stretching       389         4.13.2.4       The Ide State       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       391         4.13.2.8       Repeated Transmissions       391         4.13.3       The PC Data Format       391         4.13.5       IC Routines for the SX Controller       395         4.13.5       IC Routines for the SX Controller       394         4.13.5       The PC Master VP       406         4.13.5       The PC Master VP       407         4.13.5       The PC Master VP       408         4.13.5.4       The PC Slave VP       40                                                                                               | 4.10.2   | Quick-Scan and 2-Key Rollover                | 372 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------|-----|

| 4.12       A Software FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.10.3   | Need more Port Pins for the Keyboard Matrix? |     |

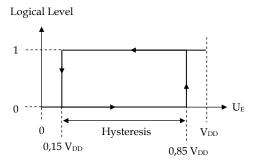

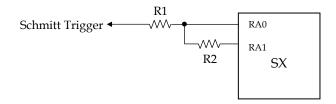

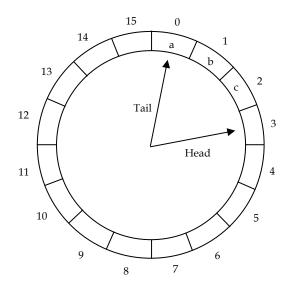

| 4.13       FC Routines       388         4.13.1       The PC Bus       389         4.13.2       The Basic PC Protocol       389         4.13.2       The Basic PC Protocol       389         4.13.2       The Basic PC Protocol       389         4.13.2.1       "Master" and "Slave"       389         4.13.2.2       The Start Condition       389         4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The PC Data Format       391         4.13.4       Bus Lines and Pull-up Resistors       394         4.13.5       PC Routines for the SX Controller       395         4.13.5.1       Common Program Modules       406         4.13.5.2       The Mainline program       407         4.13.5.4       The PC Slave VP       408         4.13.5.4       The PC Slave VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       425 <t< td=""><td>4.11</td><td>An "Artificial" Schmitt Trigger Input</td><td> 380</td></t<>                             | 4.11     | An "Artificial" Schmitt Trigger Input        | 380 |

| 4.13.1       The PC Bus       388         4.13.2       The Basic PC Protocol       389         4.13.2.1       "Master" and "Slave"       389         4.13.2.2       The Start Condition       389         4.13.2.3       Data Transfer, and Clock Stretching       389         4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The PC Data Format       391         4.13.3       The PC Data Format       391         4.13.5       PC Routines for the SX Controller       395         4.13.5.1       FC Routines for the SX Controller       406         4.13.5.2       The Mainline program       407         4.13.5.3       The PC Master VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tec                                                                                      | 4.12     | A Software FIFO                              | 382 |

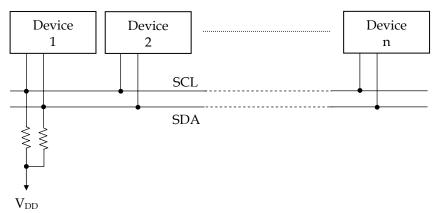

| 4.13.2       The Basic PC Protocol       389         4.13.2.1       "Master" and "Slave"       389         4.13.2.2       The Start Condition       389         4.13.2.3       Data Transfer, and Clock Stretching       389         4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The PC Data Format       391         4.13.4       Bus Lines and Pull-up Resistors       394         4.13.5       PC Routines for the SX Controller       395         4.13.5.1       Common Program Modules       406         4.13.5.2       The PC Master VP       407         4.13.5.4       The PC Slave VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tech Bot       425         4.16.1       Introduction       425         4.16.2       Controlling the SX tech Bot Servos       422         4.16.3.1                                                                                      | 4.13     | I <sup>2</sup> C Routines                    | 388 |

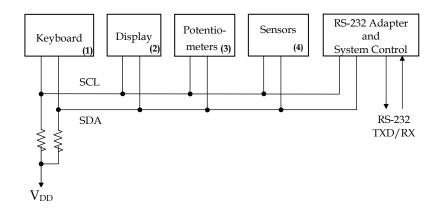

| 4.13.2.1       "Master" and "Slave"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.13.1   | The I <sup>2</sup> C Bus                     | 388 |

| 4.13.2.2       The Start Condition       389         4.13.2.3       Data Transfer, and Clock Stretching       389         4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The PC Data Format       391         4.13.4       Bus Lines and Pull-up Resistors       394         4.13.5       PC Routines for the SX Controller       395         4.13.5.1       Common Program Modules       406         4.13.5.2       The Mainline program       407         4.13.5.3       The PC Master VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tech Bot       425         4.16.1       Introduction       425         4.16.2       Control Program       429         4.16.3       The Basic Control Program       429         4.16.3.1       Calibrating the Servos       428         4.16.3       The                                                                                      | 4.13.2   | The Basic I <sup>2</sup> C Protocol          | 389 |

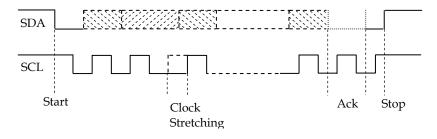

| 4.13.2.3       Data Transfer, and Clock Stretching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.13.2.1 | "Master" and "Slave"                         | 389 |

| 4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The IC Data Format       391         4.13.4       Bus Lines and Pull-up Resistors       394         4.13.5       IPC Routines for the SX Controller       395         4.13.5.1       Common Program Modules       406         4.13.5.2       The Mainline program       407         4.13.5.3       The PC Master VP       408         4.13.5.4       The FC Slave VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tech Bot       425         4.16.1       Introduction       425         4.16.2       Controlling the SX Tech Bot Servos       428         4.16.3       The Basic Control Program       429         4.16.3.1       Calibrating the Servos       433         4.16.4       Some Timing Considerations       433         4.16.5 <t< td=""><td>4.13.2.2</td><td>The Start Condition</td><td> 389</td></t<>                 | 4.13.2.2 | The Start Condition                          | 389 |

| 4.13.2.4       Acknowledge Message from the Slave       390         4.13.2.5       The Stop Condition       390         4.13.2.6       The Idle State       390         4.13.2.7       Bus Arbitration       390         4.13.2.8       Repeated Transmissions       391         4.13.3       The IC Data Format       391         4.13.4       Bus Lines and Pull-up Resistors       394         4.13.5       IPC Routines for the SX Controller       395         4.13.5.1       Common Program Modules       406         4.13.5.2       The Mainline program       407         4.13.5.3       The PC Master VP       408         4.13.5.4       The FC Slave VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tech Bot       425         4.16.1       Introduction       425         4.16.2       Controlling the SX Tech Bot Servos       428         4.16.3       The Basic Control Program       429         4.16.3.1       Calibrating the Servos       433         4.16.4       Some Timing Considerations       433         4.16.5 <t< td=""><td>4.13.2.3</td><td>Data Transfer, and Clock Stretching</td><td> 389</td></t<> | 4.13.2.3 | Data Transfer, and Clock Stretching          | 389 |

| 413.2.5       The Stop Condition       390         413.2.6       The Idle State       390         413.2.7       Bus Arbitration       390         413.2.8       Repeated Transmissions       391         413.3       The PC Data Format       391         413.4       Bus Lines and Pull-up Resistors       394         413.5       PC Routines for the SX Controller       395         413.5.1       Common Program Modules       406         413.5.2       The Mainline program       407         413.5.3       The PC Master VP       408         413.5.4       The PC Slave VP       409         4.14       A "Hardware Timer"       411         4.15       A Morse Code Keyer       413         4.16       Robotics - Controlling the Parallax SX Tech Bot       425         4.16.1       Introduction       425         4.16.2       Controlling the SX Tech Bot Servos       428         4.16.3       The Basic Control Program       429         4.16.3.1       Calibrating the Servos       432         4.16.3       The Basic Control Program       433         4.16.4       Some Timing Considerations       433         4.16.5       The SX Tech Bot's Fir                                                                                      | 4.13.2.4 |                                              |     |

| 4.13.2.6       The Idle State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.13.2.5 |                                              |     |

| 4.13.2.7       Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.13.2.6 | The Idle State                               | 390 |

| 4.13.2.8Repeated Transmissions3914.13.3The I²C Data Format3914.13.4Bus Lines and Pull-up Resistors3944.13.5I²C Routines for the SX Controller3954.13.5.1Common Program Modules4064.13.5.2The Mainline program4074.13.5.3The I²C Slave VP4084.13.5.4The I²C Slave VP4094.14A "Hardware Timer"4114.15A Morse Code Keyer4134.16Robotics - Controlling the Parallax SX Tech Bot4254.16.1Introduction4254.16.2Controlling the SX Tech Bot Servos4284.16.3The Basic Control Program4294.16.3.1Calibrating the Servos4284.16.3More Parts of the Control Program4334.16.4Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.13.2.7 |                                              |     |

| 4.13.3       The PC Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.13.2.8 |                                              |     |

| 4.13.4Bus Lines and Pull-up Resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.13.3   |                                              |     |

| 4.13.5PC Routines for the SX Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                              |     |

| 4.13.5.1Common Program Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                              |     |

| 4.13.5.2The Mainline program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.13.5.1 |                                              |     |

| 4.13.5.3The PC Master VP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 0                                            |     |

| 4.13.5.4The IPC Slave VP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                              |     |

| 4.14A "Hardware Timer"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                              |     |

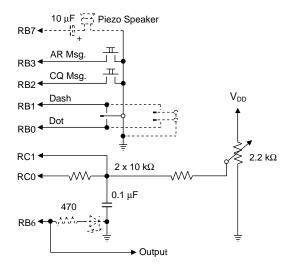

| 4.15A Morse Code Keyer4134.16Robotics - Controlling the Parallax SX Tech Bot4254.16.1Introduction4254.16.2Controlling the SX Tech Bot Servos4284.16.3The Basic Control Program4294.16.3.1Calibrating the Servos4324.16.3.2More Parts of the Control Program4334.16.4Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                              |     |

| 4.16Robotics - Controlling the Parallax SX Tech Bot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.15     |                                              |     |

| 4.16.1Introduction4254.16.2Controlling the SX Tech Bot Servos4284.16.3The Basic Control Program4294.16.3.1Calibrating the Servos4324.16.3.2More Parts of the Control Program4334.16.3Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                              |     |

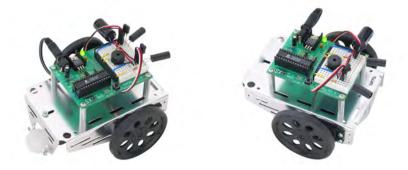

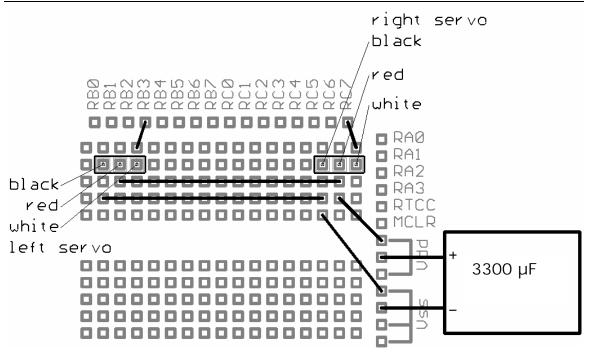

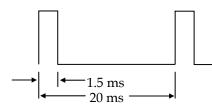

| 4.16.2Controlling the SX Tech Bot Servos4284.16.3The Basic Control Program4294.16.3.1Calibrating the Servos4324.16.3.2More Parts of the Control Program4334.16.4Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.16.1   |                                              |     |

| 4.16.3The Basic Control Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                              |     |

| 4.16.3.1Calibrating the Servos4324.16.3.2More Parts of the Control Program4334.16.3.2Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                              |     |

| 4.16.3.2More Parts of the Control Program4334.16.3Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                              |     |

| 4.16.4Some Timing Considerations4364.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                              |     |

| 4.16.5The SX Tech Bot's First Walk (in the Park)4374.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                              |     |

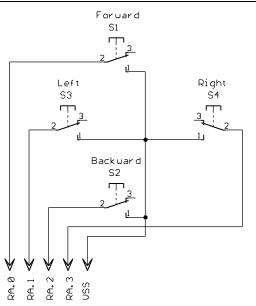

| 4.16.6Adding a "Joystick" to the SX Tech Bot4374.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                              |     |

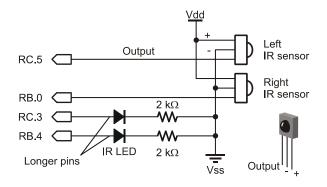

| 4.16.7The SX Tech Bot "Learns" to Detect Obstacles4394.16.7.1The Control Program for the Obstacle-Detecting SX Tech Bot442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                              |     |

| 4.16.7.1 The Control Program for the Obstacle-Detecting SX Tech Bot 442                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                              |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                              | 442 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                              |     |

| 4.17 | More Ideas for SX Tech Bot Applications | 448 |

|------|-----------------------------------------|-----|

| 5    | Index                                   | 453 |

# A Complete Guide by Günther Daubach

2<sup>ND</sup> EDITION

# **Section I - Tutorial**

# 1 Section I - Tutorial

## 1.1 Introduction

This first part of the book is intended to give you a step-by-step introduction in how to use a development system for the SX controller, and how to write the first applications for the SX.

Development systems for the SX are offered by several vendors. In this introduction, we will describe the SX-Key development system offered by Parallax.

In this text, you will find several sections that are marked in gray, together with one of the symbols below:

The exclamation mark indicates important information. You should read this text in any case to avoid problems.

This symbol marks a section that contains useful additional information, which is not necessary for understanding the current topic.

The Tutorial part of this book does not describe every feature of the SX in detail. The "R" symbol followed by a chapter and a page number indicates that more information about a topic can be found in the reference section of this book.

This symbol marks a section that contains useful additional information, which is not necessary for understanding the current topic.

Throughout the text, we have to deal with addresses, data, and values. The SX handles and stores all these in binary format, i.e. as a collection of bits where each bit can be set (1) or cleared (0). As the data memory is organized in 8-bit registers, data is always handled in bytes, i.e. in groups of 8 bits. Instead of writing binary numbers, we will use two hexadecimal digits to represent the contents of a register in most cases. The SX program memory is addressed with 12 bit values. To represent an address, we usually use three hexadecimal digits. Sometimes, when it comes to time calculations, etc. it is easier for us human beings to do the calculations in decimal. In order to distinguish between the different number types, we use the similar notation, most of the SX Assemblers allow:

A leading "%" for binary numbers, a leading "\$" for hexadecimal numbers, and no special character for decimal numbers, e.g.

$%1011\ 1100 =$ \$BC = 188

Sometimes, you may also find a notation like 0xbc, an alternative notation for hexadecimal numbers. C programmers are used to it quite well. Most available Assemblers for the SX also accept the "postfix" notation for binary, and hexadecimal values, e.g. 10010101B, or FFH, but we will not use this format in the book text.

In the tutorial example programs, we sometimes make use of instructions that are not always explained when they are used first. Please refer to the "Alphabetic Instruction Overview" in the Quick Reference section of this book when you want to learn more about the function of a specific instruction.

## 1.2 SX Development - What You Need

## 1.2.1 The Tools

When you plan to develop software and hardware for a new type of microcontroller, you usually need to buy new "tools", meaning a financial investment. For the SX, this is the case as well but fortunately, several vendors offer moderately priced development systems for the SX.

One reason why development systems for the SX can be offered cheaper than systems for other microcontrollers lies in the SX itself: It has "built-in" debugging capabilities, and due to the EEPROM program memory, and the in-system programming features, there is no need for UV EPROM erasers or in-circuit emulation systems.

## 1.2.2 Prototyping Systems

When you perform your first experiments with the SX, it is most likely that you do not have a finished PCB on hand, designed for the system you intend to develop. Various prototype boards are offered by Parallax, Ubicom, and other vendors.