#### Design Your Own Video Game Console

A Beginner's Guide to Video Game Console and Embedded System Design, Development, and Programming.

Copyright © 2004-2005 Nurve Networks LLC

#### **Publisher**

Nurve Networks LLC

#### **Author**

Andre' LaMothe

#### **Editor/Technical Reviewer**

Alex Varanese

#### **Printing**

0001

#### **ISBN**

Pending

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the user of the information contained herein. Although every precaution has been taken in the preparation of this book, the publisher and authors assume no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

#### **Trademarks**

All terms mentioned in this book that are known to be trademarks or service marks have been appropriately capitalized. Nurve Networks LLC cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark.

#### Warning and Disclaimer

Every effort has been made to make this book as complete and as accurate as possible, but no warranty or fitness is implied. The information provided is on an "as is" basis. The authors and the publisher shall have neither liability nor any responsibility to any person or entity with respect to any loss or damages arising from the information contained in this book.

The example companies, organizations, products, domain names, e-mail addresses, logos, people, places, and events depicted herein are fictitious. No association with any real company, organization, product, domain name, e-mail address, logo, person, place, or event is intended or should be inferred.

#### eBook License

This eBook may be printed for personal use and (1) copy may be made for archival purposes, but may not be distributed by any means whatsoever, sold, resold, in any form, in whole, or in parts. Additionally, the contents of the CD this eBook came on relating to the design, development, imagery, or any and all related subject matter pertaining to the XGameStation™ Micro Edition are copyrighted as well and may not be distributed in any way whatsoever in whole or in part. Individual programs are copyrighted by their respective owners and may require separate licensing.

### **Licensing, Terms & Conditions**

NURVE NETWORKS LLC, INC. END-USER LICENSE AGREEMENT FOR XGAMESTATION™ MICRO EDITION HARDWARE, SOFTWARE AND EBOOKS

YOU SHOULD CAREFULLY READ THE FOLLOWING TERMS AND CONDITIONS BEFORE USING THIS PRODUCT. IT CONTAINS SOFTWARE, THE USE OF WHICH IS LICENSED BY NURVE NETWORKS LLC, INC., TO ITS CUSTOMERS FOR THEIR USE ONLY AS SET FORTH BELOW. IF YOU DO NOT AGREE TO THE TERMS AND CONDITIONS OF THIS AGREEMENT, DO NOT USE THE SOFTWARE OR HARDWARE. USING ANY PART OF THE SOFTWARE OR HARDWARE INDICATES THAT YOU ACCEPT THESE TERMS.

GRANT OF LICENSE: NURVE NETWORKS LLC (the "Licensor") grants to you this personal, limited, non-exclusive, non-transferable, non-assignable license solely to use in a single copy of the Licensed Works on a single computer for use by a single concurrent user only, and solely provided that you adhere to all of the terms and conditions of this Agreement. The foregoing is an express limited use license and not an assignment, sale, or other transfer of the Licensed Works or any Intellectual Property Rights of Licensor.

ASSENT: By opening the files and or packaging containing this software and or hardware, you agree that this Agreement is a legally binding and valid contract, agree to abide by the intellectual property laws and all of the terms and conditions of this Agreement, and further agree to take all necessary steps to ensure that the terms and conditions of this Agreement are not violated by any person or entity under your control or in your service.

OWNERSHIP OF SOFTWARE AND HARDWARE: The Licensor and/or its affiliates or subsidiaries own certain rights that may exist from time to time in this or any other jurisdiction, whether foreign or domestic, under patent law, copyright law, publicity rights law, moral rights law, trade secret law, trademark law, unfair competition law or other similar protections, regardless of whether or not such rights or protections are registered or perfected (the "Intellectual Property Rights"), in the computer software and hardware, together with any related documentation (including design, systems and user) and other materials for use in connection with such computer software and hardware in this package (collectively, the "Licensed Works"). ALL INTELLECTUAL PROPERTY RIGHTS IN AND TO THE LICENSED WORKS ARE AND SHALL REMAIN IN LICENSOR.

- (a) You are expressly prohibited from copying, modifying, merging, selling, leasing, redistributing, assigning, or transferring in any matter, Licensed Works or any portion thereof.

- (b) You may make a single copy of software materials within the package or otherwise related to Licensed Works only as required for backup purposes.

(c) You are also expressly prohibited from reverse engineering, decompiling, translating, disassembling, deciphering, decrypting, or otherwise attempting to discover the source code of the Licensed Works as the Licensed Works contain proprietary material of Licensor. You may not otherwise modify, alter, adapt, port, or merge the Licensed Works.

- (d) You may not remove, alter, deface, overprint or otherwise obscure Licensor patent, trademark, service mark or copyright notices.

(e) You agree that the Licensed Works will not be shipped, transferred or exported into any other country, or used in any manner prohibited by any government agency or any export laws, restrictions or regulations.

- (f) You may not publish or distribute in any form of electronic or printed communication the materials within or otherwise related to Licensed Works, including but not limited to the object code, documentation, help files, examples, and benchmarks.

TERM: This Agreement is effective until terminated. You may terminate this Agreement at any time by uninstalling the Licensed Works and destroying all copies of the Licensed Works both HARDWARE and SOFTWARE. Upon any termination, you agree to uninstall the Licensed Works and return or destroy all copies of the Licensed Works, any accompanying documentation, and all other associated materials

WARRANTIES AND DISCLAIMER: EXCEPT AS EXPRESSLY PROVIDED OTHERWISE IN A WRITTEN AGREEMENT BETWEEN LICENSOR AND YOU. THE LICENSED WORKS ARE NOW PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR THE WARRANTY OF NON-INFRINGEMENT. WITHOUT LIMITING THE FOREGOING, LICENSOR MAKES NO WARRANTY THAT (i) THE LICENSED WORKS WILL MEET YOUR REQUIREMENTS, (ii) THE USE OF THE LICENSED WORKS WILL BE UNINTERRUPTED, TIMELY, SECURE, OR ERROR-FREE, (iii) THE RESULTS THAT MAY BE OBTAINED FROM THE USE OF THE LICENSED WORKS WILL BE ACCURATE OR RELIABLE, (iv) THE QUALITY OF THE LICENSED WORKS WILL MEET YOUR EXPECTATIONS, (v) ANY ERRORS IN THE LICENSED WORKS WILL BE CORRECTED, AND/OR (vi) YOU MAY USE, PRACTICE, EXECUTE, OR ACCESS THE LICENSED WORKS WITHOUT VIOLATING THE INTELLECTUAL PROPERTY RIGHTS OF OTHERS. SOME STATES OR JURISDICTIONS DO NOT ALLOW THE EXCLUSION OF IMPLIED WARRANTIES OR LIMITATIONS ON HOW LONG AN IMPLIED WARRANTY MAY LAST, SO THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU. IF CALIFORNIA LAW IS NOT HELD TO APPLY TO THIS AGREEMENT FOR ANY REASON, THEN IN JURISDICTIONS WHERE WARRANTIES, GUARANTEES, REPRESENTATIONS, AND/OR CONDITIONS OF ANY TYPE MAY NOT BE DISCLAIMED, ANY SUCH WARRANTY, GUARANTEE, REPRESENATION AND/OR WARRANTY IS: (1) HEREBY LIMITED TO THE PERIOD OF EITHER (A) Five (5) DAYS FROM THE DATE OF OPENING THE PACKAGE CONTAINING THE LICENSED WORKS OR (B) THE SHORTEST PERIOD ALLOWED BY LAW IN THE APPLICABLE JURISDICTION IF A FIVE (5) DAY LIMITATION WOULD BE UNENFORCEABLE; AND (2) LICENSOR'S SOLE LIABILITY FOR ANY BREACH OF ANY SUCH WARRANTY, GUARANTEE, JURISDICTION IF A FIVE (5) DAY LIMITATION WOULD BE UNENFORCEABLE; AINO (2) LICENSOR'S SOLE LIABILITY FOR ANY SHEACH OF ANY SUCH WARRANTY, QUARANTEE, REPRESENTATION, AND/OR CONDITION SHALL BE TO PROVIDE YOU WITH A NEW COPY OF THE LICENSED WORKS. IN NO EVENT SHALL LICENSOR OR ITS SUPPLIERS BE LIABLE TO YOU OR ANY THIRD PARTY FOR ANY SPECIAL, INCIDENTAL, INDIRECT OR CONSEQUENTIAL DAMAGES OF ANY KIND, OR ANY DAMAGES WHATSOEVER, INCLUDING, WITHOUT LIMITATION, THOSE RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER OR NOT LICENSOR HAD BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, AND ON ANY THEORY OF LIABILITY, ARISING OUT OF OR IN CONNECTION WITH THE USE OF THE LICENSED WORKS. SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF LIABILITY FOR CONSEQUENTIAL OR INCIDENTAL DAMAGES, SO THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU. THESE LIMITATIONS SHALL APPLY NOTWITHSTANDING ANY FAILURE OF ESSENTIAL PURPOSE OF ANY LIMITED REMEDY.

SEVERABILITY: In the event any provision of this License Agreement is found to be invalid, illegal or unenforceable, the validity, legality and enforceability of any of the remaining provisions shall not in any way be affected or impaired and a valid, legal and enforceable provision of similar intent and economic impact shall be substituted therefore.

ENTIRE AGREEMENT: This License Agreement sets forth the entire understanding and agreement between you and NURVE NETWORKS LLC, supersedes all prior agreements, whether written or oral, with respect to the Software, and may be amended only in a writing signed by both parties.

NURVE NETWORKS LLC 402 Camino Arrovo West Danville, CA 94506 support@nurve.net

### **Version & Support/Web Site**

This document is valid with the following hardware, software and firmware versions:

- XGS Micro Edition 1.5 or greater.

- XGS Micro Studio IDE version 1.0.

- XGS ME Programmer Unit Firmware version 1.0.

The information herein will usually apply to newer versions but may not apply to older versions. Please contact Nurve Networks LLC for any questions you may have.

Visit www.xgamestation.com for downloads, support, the access to the XGS ME user community, and more!

For technical support, sales, or to ask questions, share feedback, please contact Nurve Networks LLC at:

support@nurve.net

### Introduction

Thank you for purchasing the XGameStation™ Micro Edition! We have worked hard to provide a unique, high-quality, and educational product that will both engage and entertain. The XGameStation™ Micro Edition is the world's first do-it-yourself video game system and an empowering tool that will bring you an unprecedented level of knowledge and understanding, whether you're a hobbyist, student, or both.

This document is Chapter 11 from the work "Design Your Own Video Game Console". We have broken the book up into separate documents, so that you might load and view it more easily with lower performance systems.

### Installing the CD

The CD contains all the sources, schematics, tools, and content discussed in this document. There is no installer, simply work from the CD or drag the entire contents from the CD to your hard drive. Also, you may want to install one or more of the tools, especially *Labcenter's Proteus PCB Design Tools*, so you can look at the XGS ME designs in their native format.

Please read the README.TXT file at the root of the CD for any last minute instructions and changes. Also, each directory also has a README.TXT explaining the contents. The CD root for this content is laid out as follows:

```

XGSME_HW_CD <DIR> - The main directory/CD root for this content (may be within another

directory).

<DIR> - Contains datasheets for all chips.

\Datasheets

\General_Papers

<DIR> - Contains articles, papers, on SX and XGS programming.

\Schematics_Circuits <DIR> - Contains XGS schematics and circuits.

<DIR> - Contains SX related docs and eBooks.

\SX_Docs_Books

<DIR> - Contains Parallax Inc.'s SX-Key Software.

\SX_Key_IDE

<DIR> - Contains various tools for engineering.

\Tools

<DIR> - Contains a eBook version of "Tricks of the Windows game

Programming Gurus" and all sources.

\TricksI

<DIR> - Contains source code, demos, games.

\XGSME_Sources

\XGSME_Studio

<DIR> - Contains complete XGS ME Studio Software and manual.

\XGSME_Tutorials

<DIR> - Contains tutorials on XGS ME programming.

```

#### **WARNING!**

#### READ ONLY FLAG

This is a very important detail, so read on. When creating a CD ROM disk all the files will be written with the READ-ONLY flag enabled. This is fine in most cases unless you copy the files to your hard drive (which you will) and then edit and try to write the files back to disk. You will get a READ-ONLY protection error.

Fixing this is a snap. You simply need to clear the READ-ONLY flag on any files that you want to modify. There are 3 ways to do it. First, you can do it with Windows and simply navigate into the directory with the file you want to clear the READ-ONLY flag and then select the file, press the RIGHT mouse button to get the file properties and then clear the READ-ONLY flag and APPLY you change. You can do this with more than one file at once by selecting a group of files.

The second way is to use the File Manager and perform a similar set of operations as in the example above. The third and best way is to the Shell command:

#### ATTRIB command with a DOS/Command Shell prompt. Here's how:

Assume you have copied the entire SOURCE directory on your hard drive to the location C:\SOURCE. To reset all the READ-ONLY attributes in one fell swoop you can use the ATTRIB command. Here is the syntax:

#### C:\DIRECTORY> ATTRIB -r \*.\* /s

This instructs the command shell to clear the READ-ONLY flag "r" from all files "\*.\*" and all lower sub-directories "/s".

### **Getting Started**

Before reading this document and experimenting with the hardware and low level programming I highly recommend you read cover to cover the *XGameStation™ Micro Edition User Guide* which will help you become familiar with the tools, IDE, programming, debugging (if you have an SX-KEY), as well as other aspects of the XGS ME such as adjustments, troubleshooting, and so forth.

#### Viewing the Schematics

The XGameStation Micro Edition was designed using Labcenter's Proteus schematic entry and PCB layout tools. I consider these to be the best tools for the price and performance. If you wish to view any of the schematics for the XGS ME then you will need to install Proteus on your computer, you can find a copy of the installer in the **Tools**\ sub-directory. However, the latest version can always be downloaded from their site directly at:

http://www.labcenter.co.uk/

| Chapter 11                                                    | 8  |

|---------------------------------------------------------------|----|

| The XGS Micro Edition System Design and Programming           | 8  |

| 11.1 Introducing the XGS Micro Edition                        | 9  |

| 11.1.2 XGS Micro Edition Switches, Adjustments and Indicators | 10 |

| 11.1.2.1 The Power Switch                                     | 10 |

| 11.1.2.2 The XGS ME Power Supply                              | 10 |

| 11.1.2.3 The RESET Switch                                     | 10 |

| 11.1.2.4 The SYSMODE Switch                                   | 10 |

| 11.1.2.5 Audio Volume Adjustment                              | 11 |

| 11.1.2.6 Video Adjustments                                    | 11 |

| 11.1.2.7 Clock Adjustment                                     | 11 |

| 11.2 The XGS Micro Edition Hardware / Software Model          | 12 |

| 11.2.1 Basic Operation of the XGS ME                          | 14 |

| 11.2.1.1 The Control Bus                                      | 16 |

| 11.2.1.2 The Power Lines                                      | 16 |

| 11.2.2 Hardware Interfaces and I/O Port Mappings              | 17 |

| 11.3 Programming the XGS ME                                   | 17 |

| 11.4 Power Supply Design                                      | 19 |

| 11.4.1 The 5.0V Supply                                        | 19 |

| 11.4.2 The 3.3V Supply                                        | 19 |

| 11.4.3 The 12.5V Supply                                       | 20 |

| 11.5 Frequency Divider Circuit Design                         | 21 |

| 11.6 Joystick Design and Programming                          | 23 |

| 11.6.1 Joystick Hardware Description                          | 23 |

| 11.6.2 Reading The Joysticks                                  | 27 |

| 11.6.3 Implementing the Read Function in SX52 ASM             | 27 |

| 11.6.4 Joystick Demo                                          | 30 |

| 11.7 Keyboard Interface and Programming             | 32 |

|-----------------------------------------------------|----|

| 11.7.1 Communication Protocol from Keyboard to Host | 34 |

| 11.7.1.1 Keyboard Read Algorithm                    | 35 |

| 11.8 SRAM Architecture and Programming              | 39 |

| 11.8.1 SRAM Hardware Interface                      | 39 |

| 11.8.1.1 Random SRAM Access Bandwidth               | 42 |

| 11.8.1.2 Sequential Same Page SRAM Access Bandwidth | 42 |

| 11.8.2 Accessing the SRAM                           | 43 |

| 11.8.2.1 Address Setup                              | 44 |

| 11.8.2.2 Reading from the SRAM                      | 45 |

| 11.8.2.3 Writing to the SRAM                        | 48 |

| 11.8.3 Demo Program                                 | 51 |

| 11.8.4 Advanced Uses of the SRAM                    | 51 |

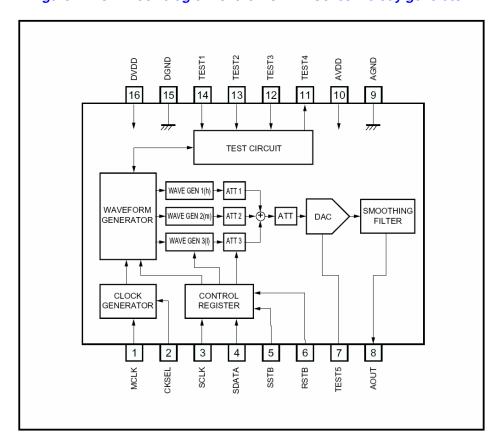

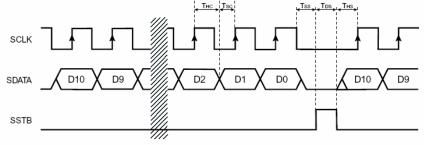

| 11.9 Sound Hardware and Programming                 | 52 |

| 11.9.1 The BU8763's Hardware Interface              | 54 |

| 11.9.2 Programming the BU8763                       | 56 |

| 11.9.2.1 The BU8763's Register Map                  | 58 |

| 11.9.2.2 Serial Sound Packet Command Driver         | 63 |

| 11.9.2.3 Sound Packet Driver Globals                | 64 |

| 11.9.2.4 The Complete Sound Packet Driver           | 64 |

| 11.9.2.5 Calling the Packet Driver                  | 66 |

| 11.9.3 Sound Demo Program                           | 66 |

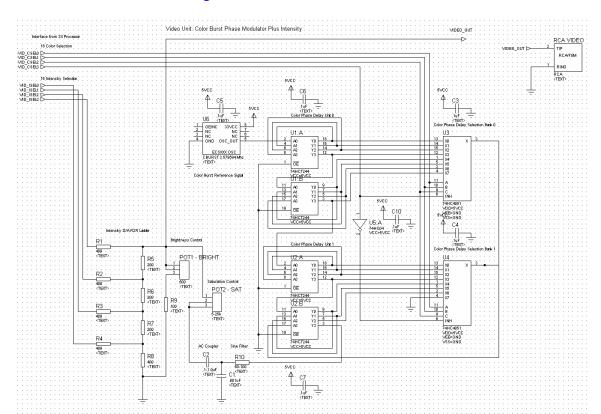

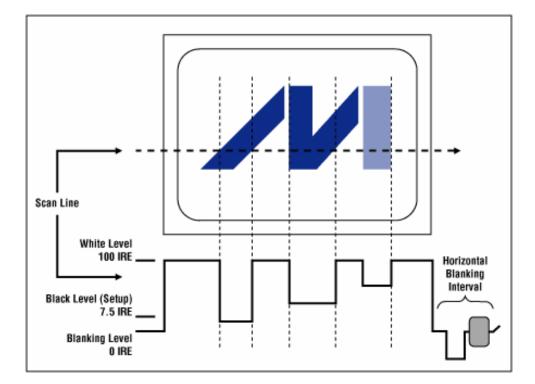

| 11.10 XGS Video Hardware and NTSC/PAL Programming   | 67 |

| 11.10.1 Video Hardware Description                  | 68 |

| 11.10.2 Review of NTSC Video                        | 69 |

| 11.10.2.1 Interlaced versus Progressive Scans       | 70 |

| 11.10.3 Video Formats and Interfaces                | 71 |

| 11.10.4 Composite Color Video Blanking Sync Interface           | 72  |

|-----------------------------------------------------------------|-----|

| 11.10.5 Color Encoding                                          | 74  |

| 11.10.6 Putting it All Together                                 | 75  |

| 11.10.6.1 Frame Construction                                    | 75  |

| 11.10.6.2 Line Construction                                     | 76  |

| 11.10.6.3 Generating B/W Video Data                             | 77  |

| 11.10.6.4 Generating Color Video Data                           | 77  |

| 11.10.6.5 NTSC Signal References                                | 78  |

| 11.11 Programming The XGS ME Video Hardware                     | 78  |

| 11.11.1 Generating a Composite Luma/Chroma Video Signal Voltage | 78  |

| 11.11.1.1 Generating Luma                                       | 78  |

| 11.11.11.2 Generating The Color Burst Signal                    | 79  |

| 11.11.11.3 Generating a Single Pixel                            | 80  |

| 11.11.2 Video Demos                                             | 82  |

| 11.11.2.1 Video Kernel Tips                                     | 83  |

| 11.11.2.1 Single Color Bar Demo                                 | 84  |

| 11.11.2.2 Color Bars Demo                                       | 90  |

| 11.11.2.3 Animated Color Bars Demo                              | 91  |

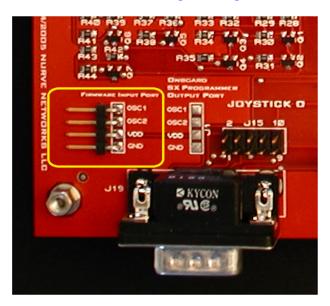

| 11.12 The Onboard Programmer                                    | 92  |

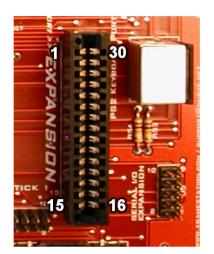

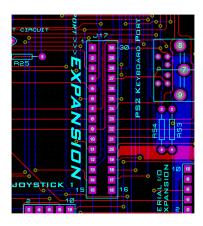

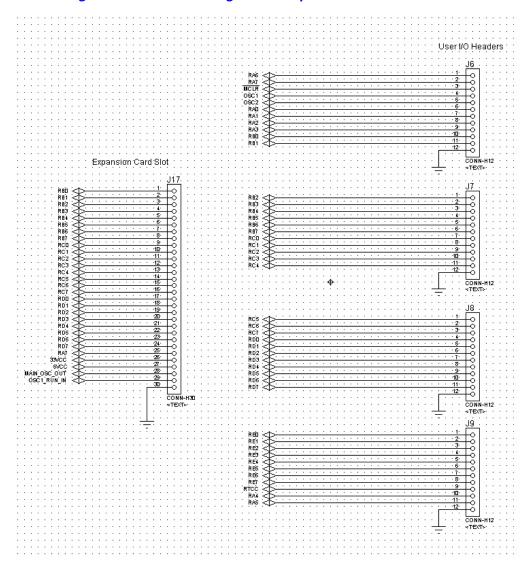

| 11.13 XGS 30-Pin Interface and SX52 Headers                     | 96  |

| 11.13.1 Expansion Slot Ideas                                    | 98  |

| 11.13.2 SX52 Headers                                            | 98  |

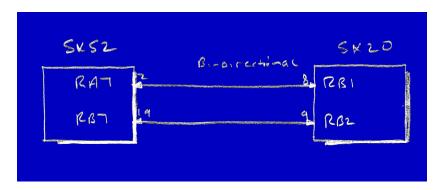

| 11.14 Multiprocessor Support                                    | 99  |

| 11.14.1 Adding Multiprocessor Support in Firmware               | 99  |

| 11.15 XGS ME Programming Tutorials                              | 100 |

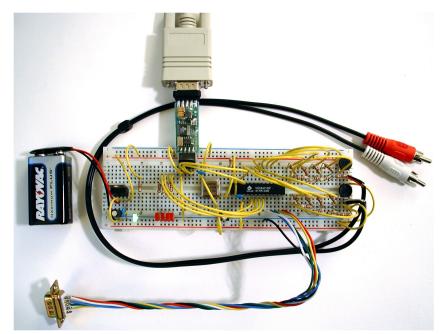

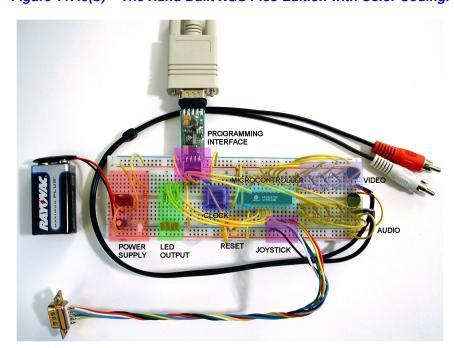

| 11.16 XGS Pico Edition – Bonus Section !!!                      | 101 |

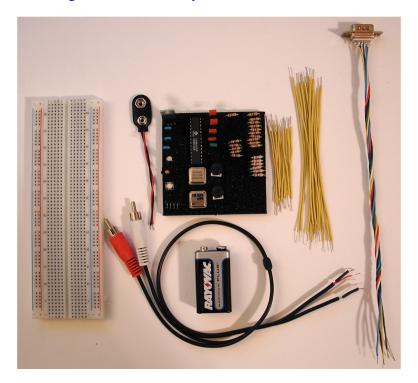

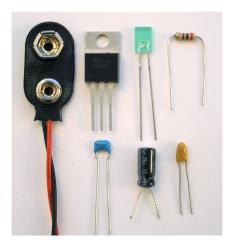

| 11.16.1 The Pico Edition Kit                                    | 103 |

| 11.16.1.1 Unpacking the Pico Edition                             | 103 |

|------------------------------------------------------------------|-----|

| 11.16.1.2 Checking the Parts List and Setting up Your Work Space | 104 |

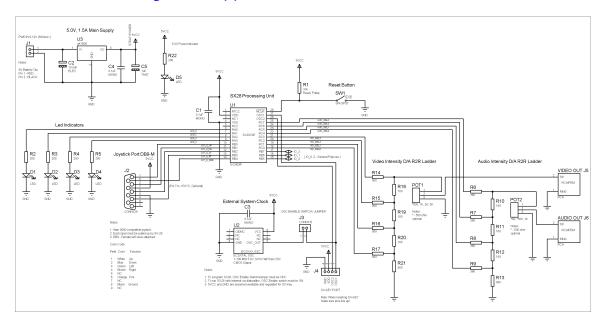

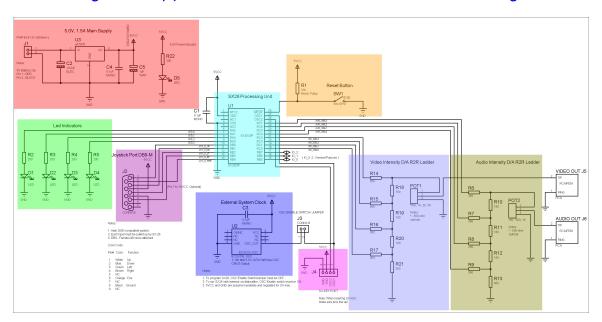

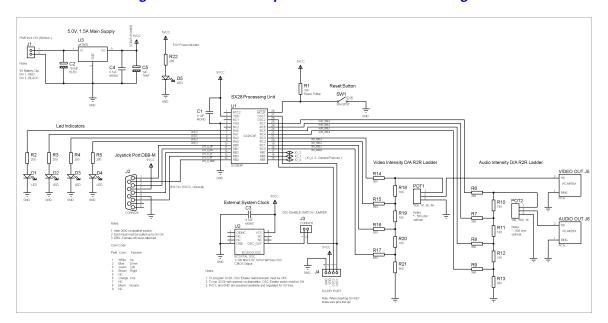

| 11.16.2 The Pico Design Files                                    | 105 |

| 11.16.3 Pico Edition Systems                                     | 106 |

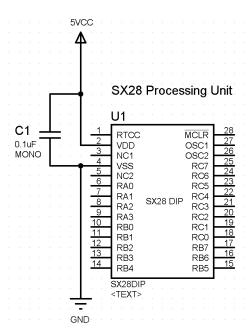

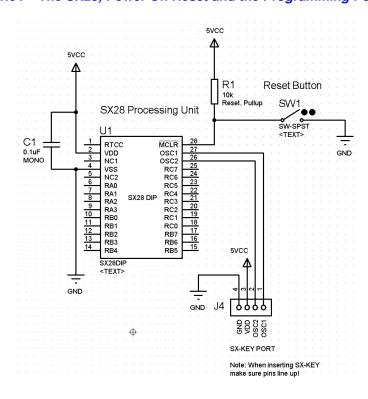

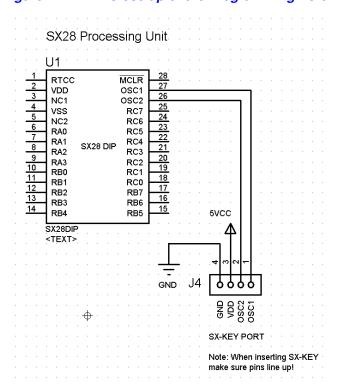

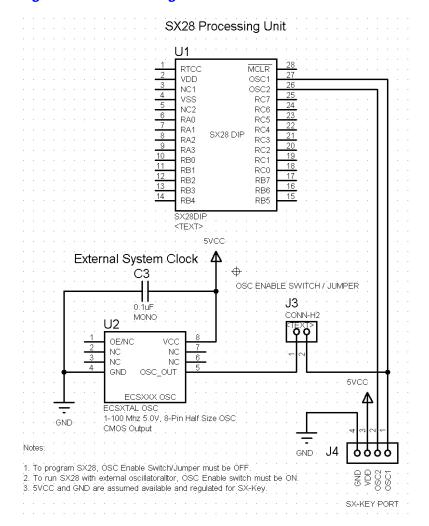

| 11.16.3.1 Processing Unit                                        | 107 |

| 11.16.3.2 Power Supply                                           | 108 |

| 11.16.3.3 Reset Circuit                                          | 109 |

| 11.16.3.4 System Clock                                           | 110 |

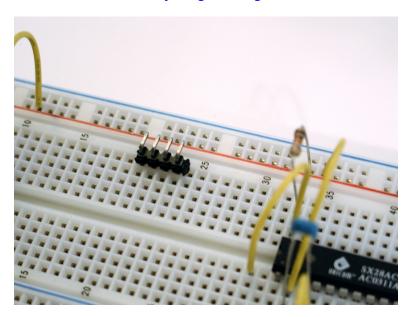

| 11.16.3.5 The Programming Port                                   | 111 |

| 11.16.3.6 I/O                                                    | 111 |

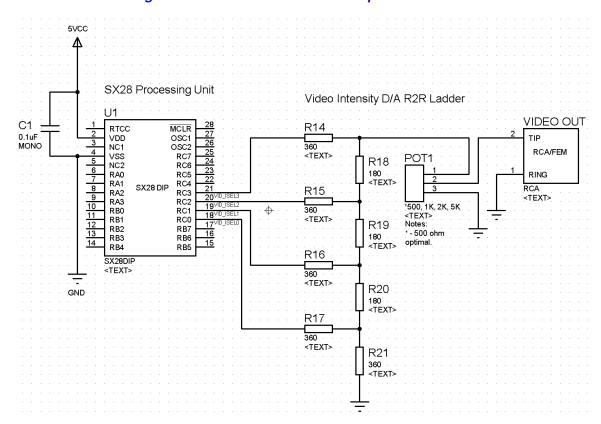

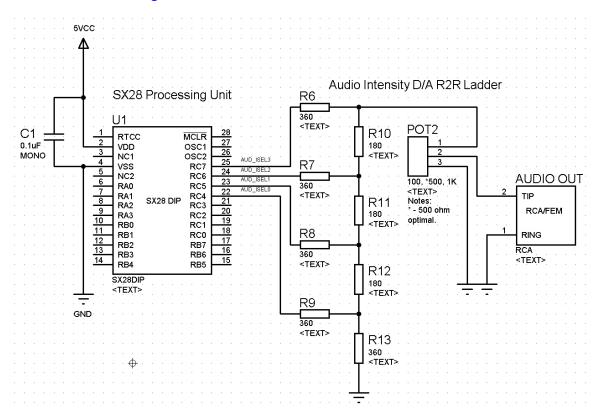

| 11.16.3.7 Graphics Hardware                                      | 115 |

| 11.16.3.8 Sound Hardware                                         | 116 |

| 11.16.4 Building the Pico Edition                                | 117 |

| 11.16.4.1 Organizing the Kit Parts and Preparing to Build        | 118 |

| 11.16.4.2 Reviewing the Solderless Breadboard                    | 119 |

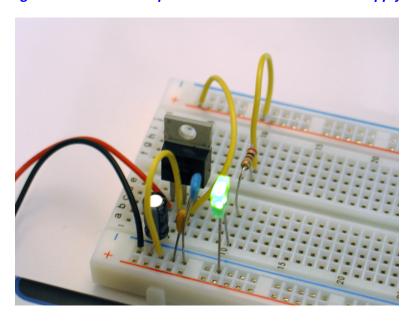

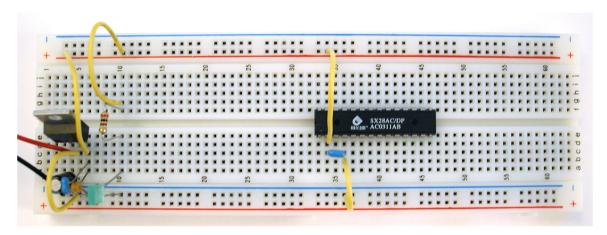

| 11.16.4.3 Building the Power Supply                              | 121 |

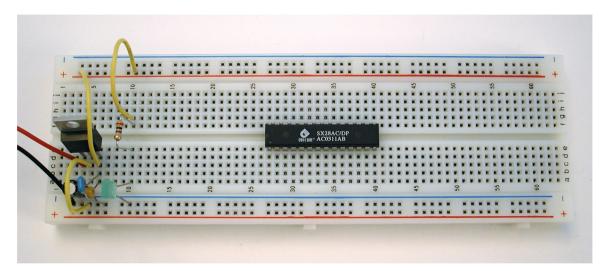

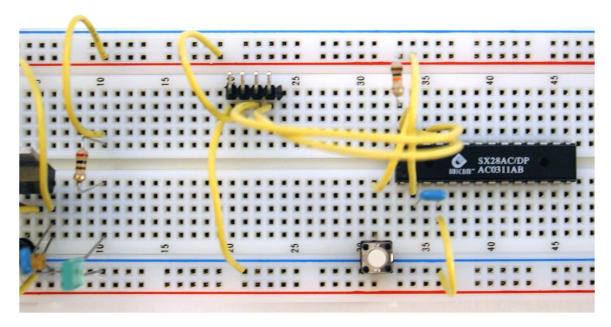

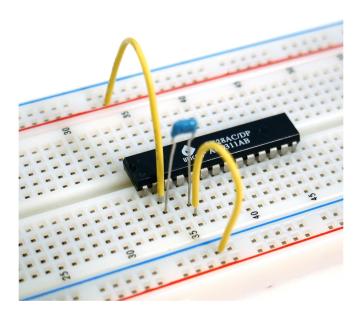

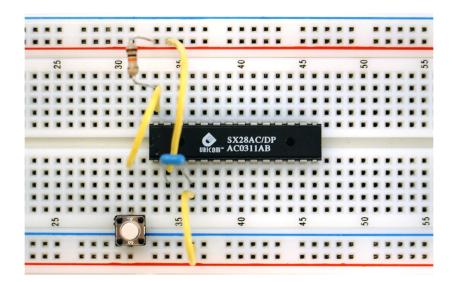

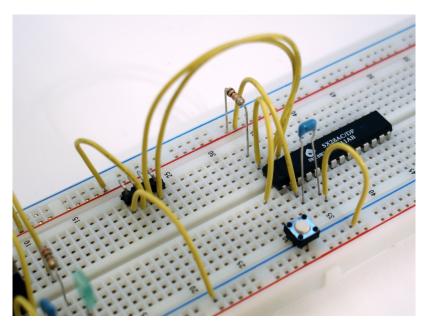

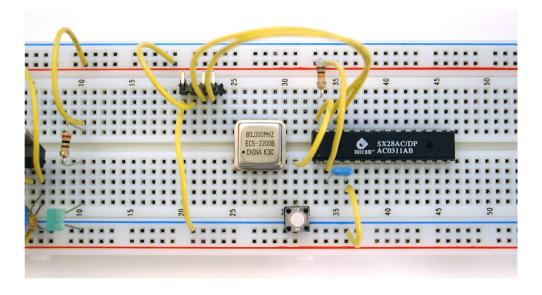

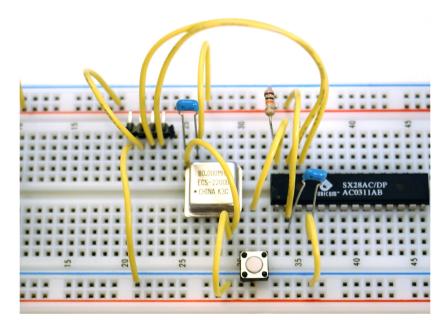

| 11.16.4.4 Adding the SX28 Processor                              | 124 |

| 11.16.4.5 Building the Clock Circuit                             | 131 |

| 11.16.4.6 Adding the LED Output Port                             | 134 |

| 11.16.4.7 Building the Video-Out R2R Ladder and Output           | 137 |

| 11.16.4.8 Building the Audio-Out R2R Ladder and Output           | 140 |

| 11.16.4.9 Adding the Joystick Port                               | 144 |

| 11.16.4.10 Final Systems Check and Wiring Review                 | 147 |

| 11.16.5 Powering the Pico Up                                     | 147 |

| 11.16.5.1 Battery or Power Supply                                | 148 |

| 11.16.5.2 System Start up and Firmware                           | 148 |

| 11.16.6 Programming the Pico                                     | 149 |

| 11.16.6.1 Loading a Program into SX-KEY              | 150 |

|------------------------------------------------------|-----|

| 11.16.6.2 Downloading and Running a Program          | 151 |

| 11.16.6.3 Changing the Clock in Real-Time            | 152 |

| 11.16.6.4 Programming Tips                           | 152 |

| 11.16.7 Blinking Light Test                          | 153 |

| 11.16.7.1 Loading and Running the LED Program        | 155 |

| 11.16.8 Joystick Programming                         | 156 |

| 11.16.8.1 Loading and Running the Joystick Program   | 158 |

| 11.16.9 Graphics Programming                         | 158 |

| 11.16.9.1 Single White Bar Demo                      | 159 |

| 11.16.9.2 Shaded Bar Demo                            | 162 |

| 11.16.9.3 Racer City Demo                            | 163 |

| 11.16.9.4 Color Video Generation on the Pico Edition | 164 |

| 11.16.9.3 Loading and Running the Graphics Demos     | 169 |

| 11.16.10 Sound Programming                           | 170 |

| 11.16.10.1 Creating Noise                            | 171 |

| 11.16.10.2 Creating Pure Tones                       | 173 |

| 11.16.10.3 Loading and Running the Sound Demos       | 179 |

| 11.16.11 Pico Edition Enhancements                   | 180 |

| Summary                                              | 180 |

| Epilog                                               | 181 |

| NOTES                                                | 183 |

# **Chapter 11**

### The XGS Micro Edition System Design and **Programming**

In this chapter, we are going to discuss everything about the XGameStation™ Micro Edition's designs, architecture, programming, and integration. This chapter is probably the most projectcentric of the book and more or less reviews the entire design and use of the system. Here are the major highlights of this chapter:

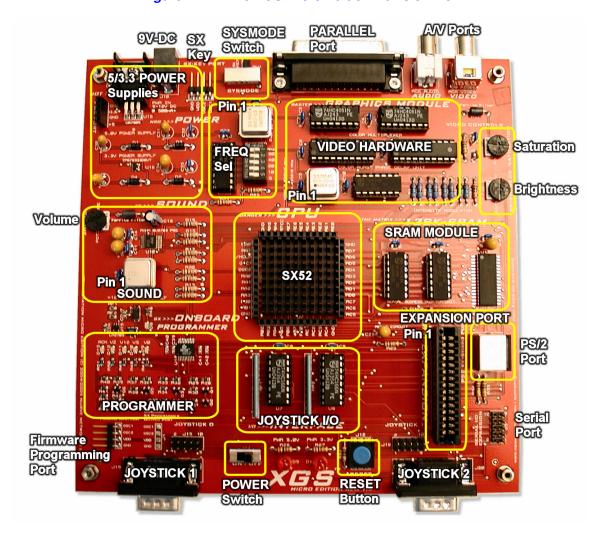

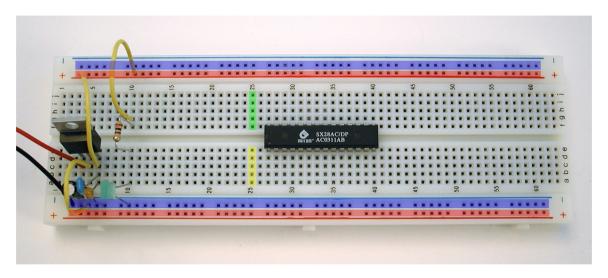

Figure 11.1 – The XGS Micro Edition Revision 1.5.

### 11.1 Introducing the XGS Micro Edition

The **XGS Micro Edition** (XGS ME) shown in Figure 11.1 is a high speed, embedded system, game console with the following features:

- A Ubicom SX52 RISC 4-deep pipelined microcontroller running at a maximum speed of 80 MHz, supporting 4K x12 bit WORDS of EEPROM program memory and 262 bytes of internal RAM. There is also an internal on chip clock that runs up to 4 MHz.

- NTSC/PAL Video generated via software control with color phase burst generation helper hardware for a total of 32 colors and approximately 10 intensities.

- 3 Channel Sound with envelop control and full coverage of the entire musical scale via the ROHM BU8763 Programmable Melody Generator.

- Atari 2600 compatible DB9 joystick inputs with extra support for other serial and parallel input devices.

- 128Kx8 of externally accessing high speed 12ns SRAM (Static RAM) via a serializing address bus and parallel data bus for a SRAM access rate of one byte per 2 clocks per 16 byte page.

- Built in support for the Parallax Inc. SX-Key programming module from http://www.parallax.com.

#### **WARNING!**

Pay close attention to the orientation of the oscillator chips, during transport they may come loose. The topmost oscillator is the main SX clock and should be 80 MHz, pin 1 is the top left pin of the socket viewing the board as shown in the figure. The video generation clock should be 3.579594 MHz (or 4.43 MHz for PAL), this oscillator chip is located to the top left of the SX processor and pin 1 is located at the bottom left of the socket. Finally, the sound oscillator located at the bottom of the ROHM melody generator chip is 5.376 MHz pin 1 is bottom left of the socket. Make sure all oscillator chips are inserted firmly, but do not force them!

The XGS ME was designed with the hobbyist in mind, so there is easy access to the pins of the SX52 via headers surrounding the SX chip as well as headers exporting out the serial interfaces from the joysticks along with a super serial interface. The XGS ME is programmed similarly to an Atari 2600, that is, the programmer controls the timings of the NTSC/PAL raster "on the fly". However, the XGS ME has some extra hardware to help with the color burst generation, so programming video more or less boils down to a deterministic loop that controls HSYNC, VSYNC, COLOR BURST, LUMA and CHROMA manually, video logic is performed during HSYNC, VSYNC, and between pixels! In most cases, all game logic; AI, sound, input will be performed during the vertical retrace period.

### 11.1.2 XGS Micro Edition Switches, Adjustments and Indicators

Referring to Figure 11.1, the XGS ME has two slide switches, one momentary reset switch, and a 5 pole DIP switch to control main clock speed into the SX52.

#### 11.1.2.1 The Power Switch

The switch at J11 Located at the **front** of the XGS ME is the power switch, simply switch it to **ON/OFF** to enable or disable power. When you switch the power on you will see the +5V and +3.3V LEDs (light emitting diodes) at the front of the board (D5 and D6) illuminate indicating "**power-good**" on both supplies. During power on the system will reset.

#### 11.1.2.2 The XGS ME Power Supply

The XGS ME takes a 9-12V 500+ mA DC supply with a 2.1 mm plug with RING = GROUND and TIP = +. 9V is the best as 12V tends to create a lot of heat in the heat sink. So, if you have to use a DC transformer from your region, make sure its 9V, 500 mA+, ring ground, tip plus.

Do NOT use an AC power supply, there is no rectification and it will destroy the XGS! Make sure the power supply is DC, however, it does NOT need to be regulated, but if it is then it will not hurt the XGS, only AC will hurt it.

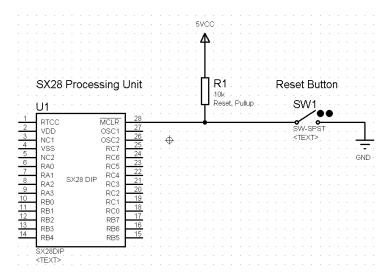

#### 11.1.2.3 The RESET Switch

Referring to Figure 11.1, the system **RESET** switch is located at the **front** of the XGS ME to the right of the power indicator LEDs at location J12. Simply press the switch anytime to reset the system.

The XGS ME also has a power-on reset circuit, so if you cycle the power the XGS will also resets itself. Nonetheless, it's a good idea to reset the XGS ME whenever you program it or put it into RUN mode to make sure the system starts up clean. Also, during reset the SX and the sound processor are reset only, the SRAM will maintain the data in it, thus you have to manually zero the SRAM if you wish it to be cleared at reset.

#### 11.1.2.4 The SYSMODE Switch

The "SYSMODE" switch is located at the **rear** of the board by the main SX clock oscillator, its labeled SW1. The "SYSMODE" switch selects one of the following modes:

**SK-KEY MODE** (SK-KEY) – Leftmost position, puts the board into SX-Key mode and accepts programs and debugging control from an inserted SX-Key.

**PROGRAM MODE** (PGM) – Middle position, puts the board into internal/on board program mode using XGS Micro Edition studio and the parallel interface cable.

**RUN MODE** (RUN) – Rightmost position, gates the main clock to the SX52 and runs it at 80, 40, 20, 10, 5 MHz (depending on the clock divider DIP Switch).

Also, when you want the XGS ME to be controlled by the serially controlled SX-KEY programming module along with the Parallax IDE then you must have the SYSMODE switch to "SX-KEY". When you have this setting then the XGS 80 MHz clock is deselected (physically gated out of the system) and the SX-KEY is allowed to talk to the SX processor. In this mode, you can use the SX-KEY to generate the clock for the SX, debug, upload software, etc. This mode is how you will develop software with the SX-Key IDE if you prefer this to the XGS Micro Edition Studio.

However, even if you set the SX-KEY and IDE for 80 MHz, you must still verify that your code timing works perfectly with the ONBOARD 80 MHz clock in the "RUN" mode since the SX-KEY generates the 80 MHz electronically and may not be as accurate as our clock. Thus, your normal coding might follow this workflow:

- **Step 1:** Code with SYSMODE switch in "**SX-KEY**" mode with SX-KEY generating clock.

- Step 2: Verify program works.

- **Step 3:** Switch SYSMODE switch to "RUN" mode and hit the RESET button at the front of the XGS ME to insure everything restarts.

- **Step 4:** Verify your program works with the onboard 80 MHz oscillator, GOTO Step 1 and continue coding.

More or less, you simply want to make an effort to make sure that you check of the system works with the onboard 80 MHz oscillator if you are doing tight video timing algorithms since the clock generated by the SK-KEY hardware might be slightly jittery.

### 11.1.2.5 Audio Volume Adjustment

Located below the clock oscillator of the sound chip is a **VOLUME** potentiometer (POT) at Pot3 that controls the volume level of the final output signal from barely audible to full volume.

#### 11.1.2.6 Video Adjustments

Most game systems simple generate NTSC/PAL video and leave it to the player to adjust the TV set to their liking, the problem with this of course is that when someone is done playing the game, the TV's display is changed and normal broadcasts look over saturated, too bright, etc. Thus the XGS ME has two very important controls; **BRIGHTNESS** at Pot 1, and **SATURATION** at Pot2. These control potentiometers are located directly under the AV (Audio / Video) ports and allow you to manually adjust them, so you don't have to play with the TV set. Brightness controls the overall brightness of the signal, and saturation controls the saturation of the color. In many case, you will find that both controls have a bit of overlap, but by adjusting both you can get any desired display you wish and without modifying the TVs settings – no more screaming moms!

#### 11.1.2.7 Clock Adjustment

The XGS ME has a clock divider circuit that allows you to divide and gate the main clock speed without changing the main oscillator chip. The 5 pole DIP switch is located right under the 80MHz oscillator and is labeled SW2. In normal cases, it will be set to 80Mhz as shown in Figure 11.1 (the topmost switch will be set to the right ON), but the other switches allow you use slower clocks, each switch gates in a clock signal that are decreasing powers of two, only one switch can be ON (to the right at once). Table 11.1 shows the frequencies to choose from.

Table 11.1 – Clock divider circuit frequency select.

| SW2 Position | Frequency into SX52 |

|--------------|---------------------|

| 1 (ON)       | 80Mhz (default)     |

| 2 (ON)       | 40Mhz               |

| 3 (ON)       | 20Mhz               |

| 4 (ON)       | 10Mhz               |

| 5 (ON)       | 5Mhz                |

NOTE

When any switch is ON (to the right), the others must be OFF (to the left).

### 11.2 The XGS Micro Edition Hardware / Software Model

The XGS ME is composed of a main MPU, the *Ubicom SX52*, a video generation module composed of basic TTL/HC logic, a I/O section to serially communicate with joysticks and other serial I/O devices, a **128K Static SRAM** module based on a serial address bus and a parallel data bus, a sound generation module based on the **ROHM BU8763** Programmable Melody Generator, a IBM PS/2 keyboard/mouse port, a 30-pin (15x2 .1" spaced edge connector for expansion), and a clock divider circuit. Each of the modules is independent of the others and can operate alone or with the other modules.

However, the system needs the MPU to control the rasterization kernel that renders the screen thus the MPU is constantly controlling the raster beam, generating sync, luma, and chroma. Nevertheless, the processor runs at **80 MHz**, meaning a clock cycle of **12.5 ns** (nanoseconds), hence, a lot of cycles can happen during the **HBLANK** (horizontal blank) and **VBLANK** (vertical blank) periods which is more than enough time for game logic and other house keeping.

As a comparison, the old Atari 2600 had hardware to help generate sprite "fragments" on a scanline basis, but still the programmer had to write the "video kernel" that was responsible for rendering and control all synchronization. The 6507 in the Atari 2600 ran at 1.79 MHz (1/2 the 3.58 MHz color burst) and was internally a 8-bit 6502 with 128 bytes of RAM and access to 4K of 8-bit ROM.

The XGS ME on the other hand runs at 80 MHz, nearly **45 times faster**, has **256 bytes** of internal RAM, has **4K of 12-bit** program memory that can be used for ROM assets and data as well. Additionally, the XGS ME has an external **128K byte SRAM** that can be used to hold procedurally generated imagery, data, and decompressed data. The XGS ME also has sound generation hardware that can produce sound and music without any MPU load. Thus, with the right programming the XGS in nearly **10x** more powerful than the Atari 2600, and hence we should be able to make it do amazing things. The demos thus far definitely attest to that.

Later in the following sections we will go into detail of each sub-system for now, let's discuss in general how the system works.

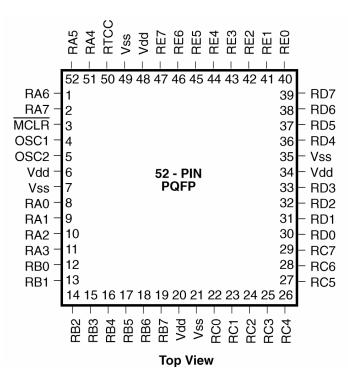

Figure 11.2 – The Ubicom SX52 Processor.

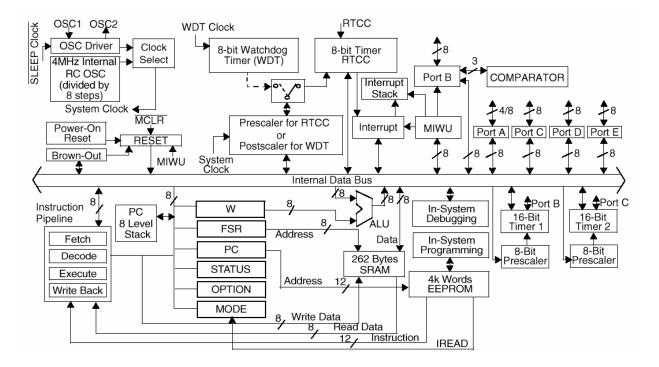

Figure 11.3 – A Block Diagram of the Internal Structure of the SX52 Processor.

### 11.2.1 Basic Operation of the XGS ME

The XGS ME's core is the SX52 processor, this is a stand alone single chip computer with a huge I/O interface, built in timers, interrupts, and much, much more. By itself the SX52 can do amazing things, but with the addition of the hardware it makes for a formidable processing unit. The chip pinout is shown in Figure 11.2, it consists of a control bus, power lines, and I/O interface. These are all detailed in datasheet document located on the CD-ROM here:

CDROOT:\XGSME HW CD\Datasheets\SX-DDS-SX4852BD-12.pdf.

Figure 11.4 – The Functional Description of the SX52 Pins.

| Name            | Pin Type     | Input Levels        | Description                                                                                |

|-----------------|--------------|---------------------|--------------------------------------------------------------------------------------------|

| RA0             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability                                |

| RA1             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability                                |

| RA2             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability                                |

| RA3             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability                                |

| RA4             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability (52-pin pkg. only)             |

| RA5             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability (52-pin pkg. only)             |

| RA6             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability (52-pin pkg. only)             |

| RA7             | I/O          | TTL/CMOS            | Bidirectional I/O Pin; symmetrical source / sink capability (52-pin pkg. only)             |

| RB0             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; comparator output; MIWU/Interrupt input                             |

| RB1             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; comparator negative input; MIWU/Interrupt input                     |

| RB2             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; comparator positive input; MIWU/Interrupt input                     |

| RB3             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; MIWU/Interrupt input                                                |

| RB4             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; MIWU/Interrupt input, Timer T1 Capture Input 1                      |

| RB5             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; MIWU/Interrupt input, Timer T1 Capture Input 2                      |

| RB6             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; MIWU/Interrupt input, Timer T1 PWM/Compare Output                   |

| RB7             | I/O          | TTL/CMOS/ST         | Bidirectional I/O Pin; MIWU/Interrupt input, Timer T1 External Event Input                 |

| RC0             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin, Timer T2 Capture Input 1                                            |

| RC1             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin, Timer T2 Capture Input 2                                            |

| RC2             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin, Timer T2 PWM/Compare Output                                         |

| RC3             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin, Timer T2 External Event Counter Input                               |

| RC4             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RC5             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RC6             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RC7             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD0             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD1             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD2             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD3             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD4             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD5             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD6             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RD7             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE0             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE1             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE2             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE3             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE4             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE5             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE6             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RE7             | I/O          | TTL/CMOS/ST         | Bidirectional I/O pin                                                                      |

| RTCC            | 1            | ST                  | Input to Real-Time Clock/Counter                                                           |

| MCLR            | i            | ST                  | Master Clear reset input – active low                                                      |

| OSC1/In/Vpp     | <u> </u>     | ST                  | Crystal oscillator input – external clock source input                                     |

| OSC2/Out        | 0            | CMOS                | Crystal oscillator output – in R/C mode, internally pulled to V <sub>dd</sub> through weak |

| 3002/0ut        |              | ONIOO               | pull-up                                                                                    |

| V <sub>dd</sub> | Р            | _                   | Positive supply pins (a total of four positive supply pins, one on each side of            |

| * aa            | '            | _                   | the device)                                                                                |

| Vss             | Р            | _                   | Ground pins (a total of four ground pins, one on each side of the device)                  |

|                 | t. O = outpu | it, I/O = Input/Out | put, P = Power, TTL = TTL input, CMOS = CMOS input,                                        |

|                 |              |                     | Multi-Input Wakeup input                                                                   |

Figure 11.3 shows a port system diagram of the SX52 chip, we are mostly interested in the 5 -I/O Ports A, B, C, D, and E. It is thru these ports that the SX52 is interfaces to the peripheral hardware of the XGS ME. Many of the Ports are standard I/O, however some of them have special functionality that is disabled if you use them for general I/O. Figure 11.4 lists the pins of the SX52. As you can see from the pin descriptions most of the port I/Os' are free for usage,

however, some ports in particular **B** and **C** have very important capabilities. For this reason in the XGS ME design I tended to leave the majority of Ports B and C alone and tried to utilize A, D, and E mostly for the design. This design allows future modifications thru the expansion port as well as hobbyists to use the ports directly since they are not connected to external hardware and minimizes conflicts.

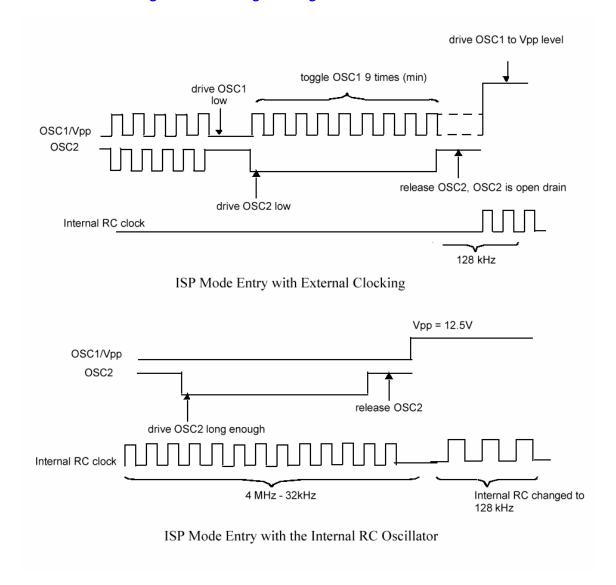

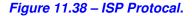

#### 11.2.1.1 The Control Bus

The control bus of the SX52 is amazing simple. It consists only of 4 lines:

RTCC - Input to the real-time clock counter, unused by the XGS ME currently.

**MCLR** – The master reset line, the XGS ME pulls this low on power up and reset, this resets the SX52.

**OSC1** – The clock input and also used as a voltage VPP (12.5V EEPROM programming voltage) programming pin when programming the SX52.

**OSC2** – Clock output when using the internal XTAL oscillator, but also used to program the SX52 and debug it.

#### 11.2.1.2 The Power Lines

Vdd, Vss – Power and ground respectively. The SX52 runs at 5.0V.

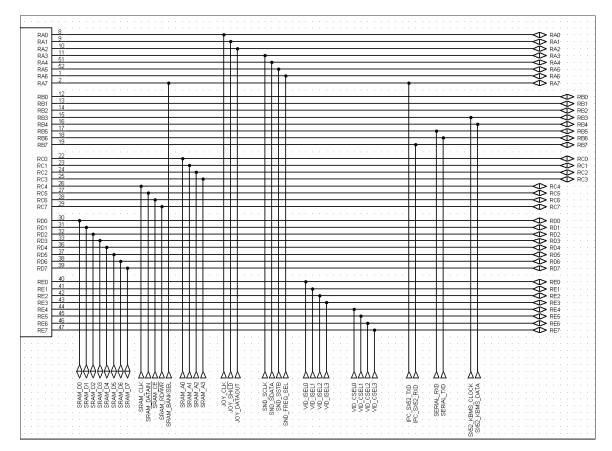

Figure 11.5 – A Schematic View of the SX52 to XGS ME Port Mappings.

### 11.2.2 Hardware Interfaces and I/O Port Mappings

The XGS ME uses a number of lines on the Ports of the SX52 as the I/O interface to each hardware sections as shown in Figure 11.5. The usage of pins was decreased by using a number of serializing hardware constructs rather than parallel for each hardware device. Not as fast in many cases, but definitely 2-3 lines is better than 9-10 lines when port bits are at a premium. In the following sections we will go into detail as to what each pin does and programming the hardware.

### 11.3 Programming the XGS ME

To save you time, I have written a number of basic demo programs that show how to access each one of the hardware modules; video, sound, joysticks, keyboard, and SRAM. The demos don't use any API per-se, but are a good starting point for you, so you don't have to reverse engineer the hardware, experiment with the timing etc., use my demos as a model of how the particular hardware works and design your own APIs. Additionally, there are a number of complete tutorials at the end of the book in the appendices by various demo coders explaining how they wrote their demos.

Now, the first thing you will learn when programming the XGS ME is that you have to write the video kernel yourself, this means that you will have to think way out of the box in ways you probably have never though before unless you have programmed on Atari 2600 like hardware.

### INTERESTING FACT

At the peak of Atari in the 80's it was estimated only 100 programmers in the world had the skill to do it, so this isn't easy – but if you look at the Atari 2600 games and realize they had a system 45x slower than the XGS ME, programmed via timeshare with a teletype and did the games in weeks to months by themselves with no team, then you will quickly realize anything is possible.

However, the point is that this kind of coding is "Black Art", your rendering loop must have a completely deterministic timing structure, so no matter which way something branches, the clocks must be the same, etc. I will discuss architectures and algorithms later in the video chapters on this kind of thinking, but it's very easy once you get the hang of it, and a lot of fun figuring out ways to squeeze more out of the cycles and hardware. Finally, since it is so hard part of our job is to find methods and abstractions to make it easier to program.

So in essence to program the XGS ME, you write your code with the IDE (either the XGS Micro Edition Studio or SX-Key), you directly control the video, audio, joysticks, and SRAM, upload your demo or game to the system and let it run.

This section has hopefully has given you a general landscape of the XGS ME hardware and its interfaces to the various hardware sub-systems. Now, let's jump into actually programming each hardware section. We will start with the easiest hardware (the joystick) and work our way to the hardest (the video system). Once you have read all these section you can finally start coding!

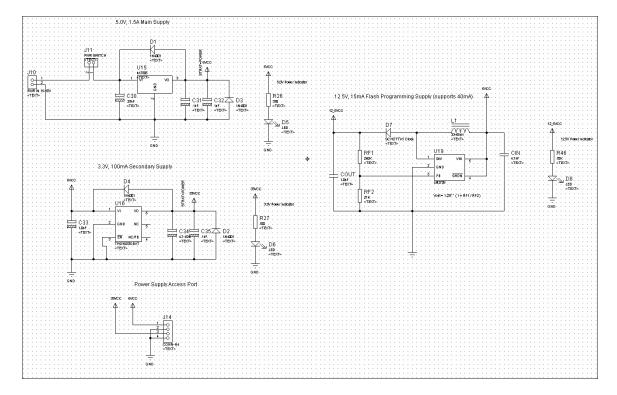

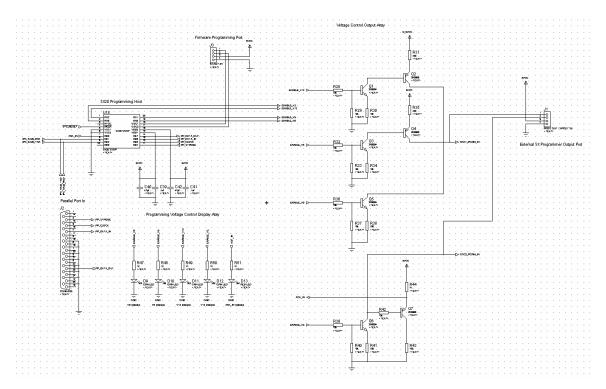

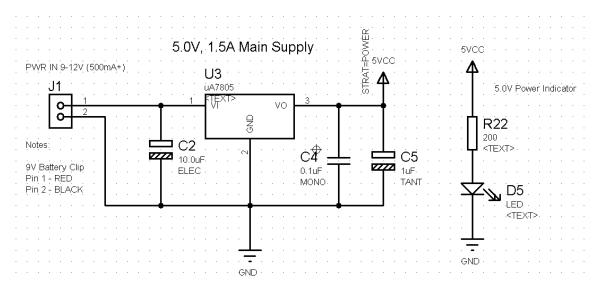

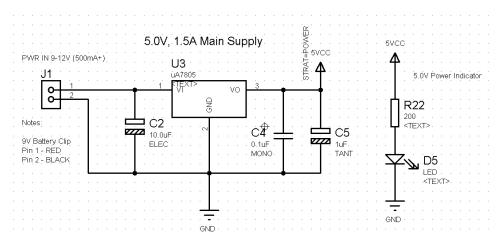

Figure 11.6 - The XGS Micro Edition's Power Supplies.

### 11.4 Power Supply Design

The XGS ME has three power supplies actually; +5V, +3.3V, and +12.5V. If you take a look at Figure 11.6 the design for all three power supplies. The Proteus design file for the power supplies is located on the CD at:

CDROOT:\XGSME HW CD\Schematics Circuits\xgs micro power 05.DSN

### 11.4.1 The 5.0V Supply

The primary power supply for the XGS ME is the *5.0V* supply consisting of the *LM7805* at *U15*. This is a generic 5.0V regulator with a 1.0-1.5A output. The unregulated DC 9-12V comes it at J10 and then is regulated by this regulator. Notice that the 7805 has short protection and reverse voltage protection diodes as well as the standard filtering capacitors. The data sheet for the 7805 is located on the CD here:

#### CDROOT:\XGSME HW\_CD\Datasheets\ua7805.pdf

Also, notice on the XGS the 7805 is heatsinked with a black aluminum sink. Although, the regulator would work without it, it would burn fingers to the touch. In fact, try touching it you will find that it's uncomfortable hot, without the heatsink it would definitely burn your fingers!

The XGS ME itself pulls 400-500ma, but the 7805 is rated for 1.5A (however I wouldn't pull much over 1.0A with the current heatsinking).

### 11.4.2 The 3.3V Supply

The *3.3V* supply is second in line of importance, but ironically only powers a single chip; the *ROHM BU8763*. In fact, I could have completely omitted the 3.3V and powered the ROHM chip with a Zener diode based regulator since it has such modest current requirements. However, in the future many hobbyists (including myself) will want to create add on cards that need 3.3V, so the 3.3V regulator will pay off in the future. With that in mind, the 3.3V regulator that was selected is a cool little chip manufactured by *Texas Instruments* called the *TPS76933DBVT* (the DBVT part is the package). It's a small package SMT device with a SOT footprint located on the board at *U16* as shown in Figure 11.1. The TPS isn't powered from the main lines, but from the 5.0V supply itself, the TPS is daisy chained from the 5.0V supply. This is not because it was easier or more convenient, but by design. The TPS will dissipate more power depending on the input voltage, so there is no need to have a large input voltage driving the TPS, all that is needed is a volt or two over 3.3V and the TPS will be able to regulate with very little power consumed for the regulation.

TIP

In general, give your regulators as much input voltage they need, but try not to drive them with the max, always try to find a source that is somewhere between the min and max recommended input voltage. Driving with too high an input even if it's within the max input voltage limit will cause extra power consumption and heat dissipation.

Additionally, the TPS is short and reverse voltage protected as was the 7805. The complete data sheet of the TPS is located on the CD here:

CDROOT:\XGSME HW CD\Datasheets\tps76933.pdf

Also, if you're planning on using 3.3V to power expansion cards plugged into the 30-pin expansion port, you can safely pull 50-75ma out of the 3.3V supply port exported to the 30-pin expansion port.

### 11.4.3 The 12.5V Supply

The *12.5V* supply gave me the most headaches in the power system design. The dilemma was more or less this; the 12.5V supply isn't for general use, but for programming the SX52. Since the SX52 uses FLASH ROM for its internal program memory, a high voltage is needed to program it. Now, there are two ways to get this voltage; step and step down. The step down method is more straightforward and is how the other two regulators work. A voltage higher than the 12.5V must be brought into the system, maybe 16-18V this then would be regulated down to 12.5V with a fixed or adjustable regulator. The only problem is that its VERY hard to find a 12.5V fixed regulator, so a variable regulator has to be used which means extra parts. But, the really bad news is that a 14-18V transformer must be used as the input to the XGS ME, this is not only expensive, but would cause a lot of heat dissipation and more board space. The 18V unregulated DC would come in, be regulated down to 12.5V then that would be used to feed the 5.0V regulator (which is actually a bit on the high side, 7-9V is preferred), so bottom line is that more power, more heat all the way around – bad choice.

The other solution is to use what's called a "*DC-DC Step-Up Converter*" that can take a lower voltage and create a higher voltage. This is accomplished thru a high frequency charge/discharge cycle. This sounds like a lot of drama, but in the end this was the better choice and the XGS ME uses a *National Semiconductor LM2705* Step-Up regulator shown in Figure 11.1. The complete data sheet is located on the CD here:

#### CDROOT:\XGSME\_HW\_CD\Datasheets\LM2705.pdf

The interesting thing about the LM2705 is that you can set the final output voltage up to 20V regardless of input which can be anywhere from 2.2 – 7.0V. Referring to the datasheet, the output voltage is a function of a pair resistors and the formula is shown below:

$$R1 = R2*(Vout/1.237 - 1)$$

rearranging and solving for Vout we get,

$$Vout = 1.237*(R1/R2 + 1)$$

The XGS ME uses R1 = 243K, R2 = 26.7K resulting in a nominal voltage of:

Vout =

$$1.237*(243K/26.7K + 1) = 12.495$$

The operation of the LM2705 is actually quite fascinating, I recommend you read it since this LM2705 and related families are a great way to get high voltages out of low voltages without much fuss, of course their current drive is limited (50-150ma in most cases).

NOTE

The 12.5V supply is *not* exported out to the 30-pin expansion slot since the current rating on the supply is so low and if an outside source pulls more than 20-30ma it will decrease the voltage to a point that the onboard programmer might not be able to function properly.

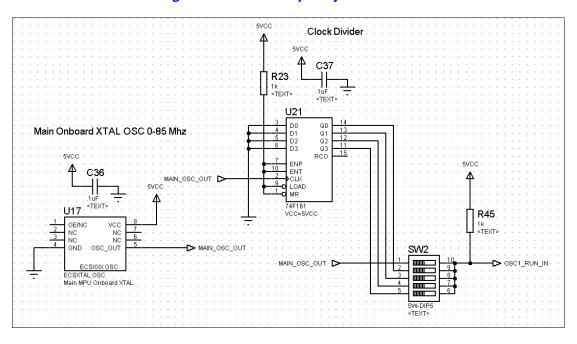

Figure 11.7 – The Frequency Divider Circuit.

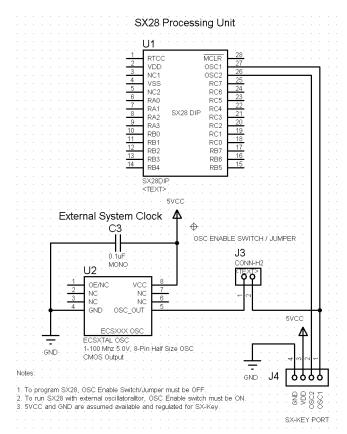

### 11.5 Frequency Divider Circuit Design

The frequency divider circuit is shown in Figure 11.7, it consists of three parts more or less; a clock source U17, the binary counter (74F161) at U21, and a 5 pole DIP switch at SW2. The circuit's purpose is to allow the user to select 80, 40, 20, 10, or 5Mhz as the input into the XGS ME with a simple DIP switch. The operation the of the circuit is as follows; the clock source at U17 is used to clock the 4-bit binary up counter U21, then signal taps are taken from each of the bit positions Qa, Qb, Qc, Qd, in essence these signals are each toggling at 1/2 the rate of the previous, so at the output of Qa is a square wave with frequency f/2 where f is the input clock, similarly at Qb there is a square wave with frequency f/4, and so forth thus:

Qa(f) = f/2

Qb(f) = f/4

Qc(f) = f/8

Qd(f) = f/16

With an input frequency f of 80Mhz this results in:

Qa(80Mhz) = 80Mhz / 2 = 40Mhz

Qb(80Mhz) = 80Mhz / 4 = 20Mhz

Qc(80Mhz) = 80Mhz / 8 = 10 MHz

Qd(80Mhz) = 80Mhz / 16 = 5 MHz

These signals along with the original 80Mhz are connected to the inputs of the 5 pole DIP switch and are mechanically gated to the main clock output labeled OS1\_RUN\_IN. Only **one** switch should be "**On**" (to the right) at a time. The switch map is shown in Table 11.2.

Table 11.2 - Frequency Selection Switch Settings

| Switch (ON) | Frequency |

|-------------|-----------|

| SW1         | 80Mhz     |

| SW2         | 40Mhz     |

| SW3         | 20Mhz     |

| SW4         | 10Mhz     |

| SW5         | 5Mhz      |

The SX52 can also be put into internal oscillator mode with the frequency directives OSC32KHZ, OSC128KHZ, OSC1MHZ, OSC4MHZ. These along with the external clocking give the XGS ME a complete range of operating frequencies.

You might be wondering why there is even a clock divider to slow the XGS ME down? The reason is two fold; first you might want to use a slower clock to make timing calculations easier. For example, a 10Mhz clock makes timing very easy since each clock is exactly 100ns. But, the more important reason why to slow the clock down is to decrease the power consumption of the hardware. CMOS circuits only consume power (for the most part) during transitions from one state to another, so the faster you clock the system the more transitions the hardware is going to make.

Of course, the first key component is the SX52 which you will find consumes the most power in the system, thus if you cut you clock to 40Mhz you will find that the total power in the system is not halved, but maybe decreases by 20-30% (some systems aren't clocked directly) which might make all the difference in a battery operated environment. For example, I have a 6 pack of AA batteries I used to make a battery pack for the XGS ME, so I can be portable, they last a couple of hours at 80Mhz, at 40Mhz, I could get maybe 3 hours out of the system.

### 11.6 Joystick Design and Programming

In this section, we are going to discuss both the hardware and the programming of the XGS ME's joystick interface, much of this should be review from the previous chapter, so you should feel right at home.

Figure 11.8 – Atari 2600 DB-9 Connector Pinouts.

```

Pin Color

Function

1

White

Uр

Blue

Down

Green

Left

4

Brown

Right

no contact

6

Orange

Fire button

7

+5V, max. 50 mA

Red

Black

Ground

8

q

no contact

```

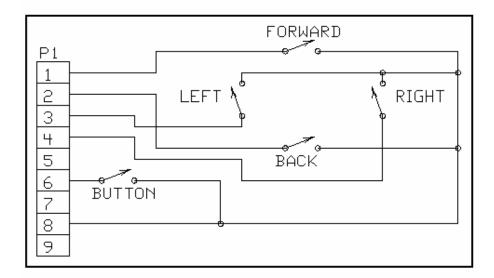

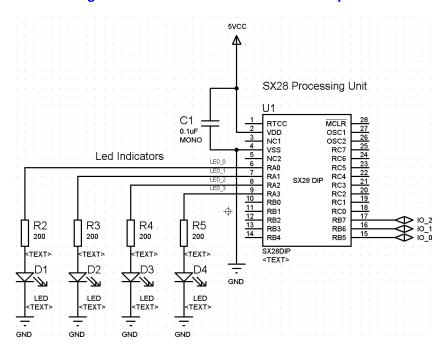

### 11.6.1 Joystick Hardware Description

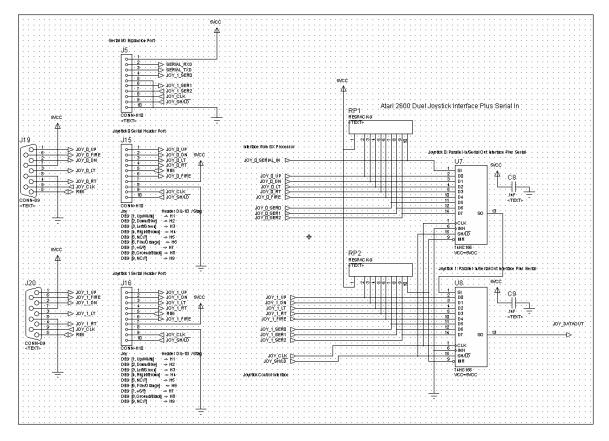

The XGS ME joystick interfaces are pin compatible with the *Atari 2600/VCS* pin outs. There are four directional buttons, and one fire button in each stick that "grounds" the input when activated. Thus, for an interface to work all these inputs must be pulled "*HIGH*" so the joystick changes can pull them low. Figure 11.8 depicts the Atari 2600 joystick interface pinouts. Considering that each joystick has 5 switches that must be read that would be 10 I/O lines from the SX52 which is unacceptable, thus the joysticks are serialized thru a pair of *74HC166* parallel to serial shift registers that are daisy chained. Figure 11.9 shows the complete design of the joystick interface, it's a bit hard to see, so the Proteus design file is also available on the CD at:

CDROOT:\XGSME HW CD\Schematics Circuits\xgs micro joystick 05.DSN

Figure 11.9 – The Complete Joystick Input Design.

You can follow along with the design using either reference. Referring to Figure 11.9 and the design file for the joysticks, the joysticks are interfaced via J19 and J12, the inputs from the joysticks are connected to the parallel inputs of the 74HC166 parallel in-serial out chips at U7 and U8. Also, notice the pull up resistor packs RP1 and RP2, these keep all the inputs HIGH until the user grounds an input by moving the stick or firing a button. Also, notice on the DB9 joystick inputs a couple extra signals have been ported to the sticks for extra functionality; JOY\_CLK and RB5, they are semi arbitrary. Also, the first page of the 74HC166's data sheet is shown in Figure 11.10 and you can find the complete data sheet on the CD-ROM at:

CDROOT:\XGSME HW CD\Datasheets\74HC HCT166 CNV 2.pdf

#### Figure 11.10 - The 74HC166 Datasheet.

**Philips Semiconductors**

Product specification

#### 8-bit parallel-in/serial-out shift register

#### 74HC/HCT166

#### **FEATURES**

- · Synchronous parallel-to-serial applications

- · Synchronous serial data input for easy expansion

- · Clock enable for "do nothing" mode

- · Asynchronous master reset

- · For asynchronous parallel data load see "165"

- · Output capability: standard

- · Icc category: MSI

#### GENERAL DESCRIPTION

The 74HC/HCT166 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT166 are 8-bit shift registers which have a fully synchronous serial or parallel data entry selected by

an active LOW parallel enable ( $\overline{PE}$ ) input. When  $\overline{PE}$  is LOW one set-up time prior to the LOW-to-HIGH clock transition, parallel data is entered into the register. When  $\overline{PE}$  is HIGH, data is entered into the internal bit position  $Q_0$  from serial data input ( $D_s$ ), and the remaining bits are shifted one place to the right ( $Q_0 \to Q_1 \to Q_2$ , etc.) with each positive-going clock transition.

This feature allows parallel-to-serial converter expansion by tying the  $Q_7$  output to the  $D_s$  input of the succeeding stage.

The clock input is a gated-OR structure which allows one input to be used as an active LOW clock enable  $(\overline{CE})$  input. The pin assignment for the CP and  $\overline{CE}$  inputs is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of input  $\overline{CE}$  should only take place while CP is HIGH for predictable operation. A LOW on the master reset (MR) input overrides all other inputs and clears the register asynchronously, forcing all bit positions to a LOW state.

#### QUICK REFERENCE DATA

GND = 0 V;  $T_{amb} = 25 \, ^{\circ}C$ ;  $t_r = t_f = 6 \, \text{ns}$

| SYMBOL                              | PARAMETER                                                   | CONDITIONS                                    | TYPICAL  |          |          |

|-------------------------------------|-------------------------------------------------------------|-----------------------------------------------|----------|----------|----------|

|                                     |                                                             |                                               | нс       | нст      | UNIT     |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CP to Q <sub>7</sub> MR to Q <sub>7</sub> | C <sub>L</sub> = 15 pF; V <sub>CC</sub> = 5 V | 15<br>14 | 20<br>19 | ns<br>ns |

| f <sub>max</sub>                    | maximum clock frequency                                     | Ī                                             | 63       | 50       | MHz      |

| Cı                                  | input capacitance                                           |                                               | 3.5      | 3.5      | pF       |

| C <sub>PD</sub>                     | power dissipation capacitance per package                   | notes 1 and 2                                 | 41       | 41       | pF       |

#### Notes

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$P_D = C_{PD} \times V_{CC}{}^2 \times f_i^{} + \Sigma \; (C_L \times V_{CC}{}^2 \times f_o)$  where:

f<sub>i</sub> = input frequency in MHz

fo = output frequency in MHz

$\sum (C_L \times V_{CC}^2 \times f_o) = \text{sum of outputs}$

C<sub>L</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I$  = GND to  $V_{CC}$ For HCT the condition is  $V_I$  = GND to  $V_{CC}$  – 1.5 V

#### ORDERING INFORMATION

See "74HC/HCT/HCU/HCMOS Logic Package Information".

December 1990

2

Reading the joysticks is rather easy with this arrangement. The SX52 latches the joysticks data into the shift registers with 3 extra bits per each shift registers (unused now, but useful for more advanced input devices) and then shifts the data out bit by bit by controlling the clock line on the shift registers. Thus, to read both joysticks the steps are to first latch the parallel data from the

joystick switches and then enter into a shifting loop where each bit of the 16-bit data word is serially shifted into the SX52 for processing. Table 11.3 illustrates the bit mappings for the joystick data word.

Table 11.3 - Joystick Data Word Mapping

| Serial Register Bit  | Description                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| d0<br>d1<br>d2<br>d3 | Joystick 0 – UP. Joystick 0 – DOWN. Joystick 0 – LEFT. Joystick 0 – RIGHT.                                                      |

| d4                   | Joystick 0 – FIRE.                                                                                                              |

| d5<br>d6             | Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 1. Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 2. |

| d7                   | Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 3.                                                                 |

| d8                   | Joystick 1 – UP.                                                                                                                |

| d9<br>d10            | Joystick 1 – DOWN.<br>Joystick 1 – LEFT.                                                                                        |

| d11                  | Joystick 1 – RIGHT.                                                                                                             |

| d12                  | Joystick 1 – FIRE.                                                                                                              |

| d13                  | Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 4.                                                                 |

| d14                  | Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 5.                                                                 |

| d15                  | Extra Serial Bit Exported to Serial I/O Expansion HDR J5-Pin 6.                                                                 |

When you read the data word simply mask off bits 5-7 and 13-15 and then the remaining low byte contains joystick 0's state and the high byte contains joystick 1's state.

The control of the joystick interface is accomplished via only 3 pins from the SX52 they are listed below in Table 11.4.

Table 11.4 – The Joystick Hardware Port Mapping Bits.

| Port Bit | XGS ME Bit | Description                                                                                   |

|----------|------------|-----------------------------------------------------------------------------------------------|

| RA0      | JOY_CLK    | Controls the clocks of the shift registers.                                                   |

| RA1      | JOY_SH/nLD | Controls the shift registers mode of operation.<br>0=Parallel Load mode, 1=Serial Shift Mode. |

| RA2      | JOY_DATOUT | As the data is shifted out it is available to the SX52 on this pin.                           |

**NOTE**

If you see a lowercase "n" in front of a signal or a "/", it means "Active LOW". In Table 11.4 for example, the signal JOY\_SH/nLD has two meanings; if 1 then it selects serial shift, if 0 it means parallel load.

### 11.6.2 Reading The Joysticks

The joysticks must be read at the same time since they are both serialized in the same data stream. The steps to read the joysticks are outlined below:

**Step 1**: Place the joystick hardware into "latch" mode, so it can latch the state of the joysticks in the serial shift registers:

```

JOY_SH/nLD = 0

```

**Step 2**: Pulse the clock line of the serial registers to actually latch the data (all operations are synchronous, thus occur when there is a complete clock pulse)

```

JOY_CLK = 0, Delay, JOY_CLK = 1, Delay. JOY_CLK = 0

```

Where Delay is in ns (nanoseconds) and is determined by the maximum clock rate of the shift registers, a value of 10-20 ns or 1-2 clocks at 80 MHz is sufficient for the current XGS ME hardware to settle.

**Step 3**: Prepare to read in the 16-bits of joystick data in the format outlined in Table 11.4. Data is shifted out at the MSB, so the first data bit available on **JOY\_DATAOUT** will be d15. To read the data, the shift registers must be placed into "shift" mode:

```

JOY_SH/nLD = 1

```

**Step 4**: Read the data bits into a bit vector:

```

for (t=0; t < 15; t++)

{

/ read the data

data[t] = JOY_DATOUT;

// clock the next bit out

JOY_CLK = 0, Delay, JOY_CLK = 1, Delay. JOY_CLK = 0

} // end for t</pre>

```

Step 5: Mask and use data.

### 11.6.3 Implementing the Read Function in SX52 ASM

Next let's take a look at an actual implementation of the read function that is excerpted from the demo later in the chapter. The code uses a number of defines that represent the various bit encodings. These defines are shown below:

Next there are a few globals that the read function passes values back and forth from the caller:

```

; general data16 ds 1 ; general 8/16 bit data vars data8 ds 1

```

Below is the actual read function, it is heavily commented and follows the read algorithm exactly.

```

Read_Joysticks

this function reads in the joysticks, again, the only timing bottleneck is the shift registers (74Hc166) which have a maximum clock speed of approx. 25 MHz! so we need to make sure that at a clock of 80 MHz, the delays are large enough for the clock, setup, hold, etc. times of the serial chips not to be violated currently the function works up to 80 MHz

the function works in the following steps

step 1: latch the data from joy 0 and joy 1 into the serial registers step 2: shift the 16-bits of data out of the shift registers representing the joysticks button states into the SX52

; step 3: return the data

; parameters on entry

; return values

data8 - byte holds left joystick [ X | X | X | X | UP | DN | RT | LT | FIRE ] data16 - byte holds right joystick [ X | X | X | X | UP | DN | RT | LT | FIRE ]

; data8

; SX52 port bit mappings

-> JOY_CLK

-> JOY_SH/LD

;RA0

;RA1

:RA2

-> JOY_DATAOUT

; step 1: read in port and mask control bits

W, RA

W, JOY_PORT_MASK

and

; step 2: prepare for read

W,#(JOY_PORT_CLK_0 | JOY_PORT_SH_nLD_0)

RÁ, W

mov

; step 3: latch joysticks into shift registers

clrb

RA<sub>-</sub>1

; JOY_SH/LD = (0), set parallel load mode

DELAY(1)

setb

RA.0

; JOY\_CLK = (1), clock

DELAY(1)

c1rb

; JOY\_CLK = (0), clock

RA.O

DELAY(1)

```

```

; step 4: shift data into system, 16-bits

RA.1

; JOY_SH/LD = (1), set serial shift mode

setb

; shift 16-bits of address into latch mov Count1, #16 ; 16 bits per joystick read

mov

:Read_Joy_Bit_Loop

; rotate results right thru carry ; rotate upper results from from including carry

r٦

data8

data16

; read joy in data on port bit first

RA.2

sb

; jump over if set

:Joy_Bit_Zero

; bit set, write 1 to joystick results packet

data8.0 ; data8[8] = (1)

:Joy_Clock_Next_Bit

setb

jmp

:Joy_Bit_Zero

; bit clear, write 0 to joystick results packet

: data8[7] = (0)

:Joy_Clock_Next_Bit

; clock next data bit

DELAY(1)

setb

; JOY\_CLK = (1), clock

RA.0

DELAY(1)

c1rb

RA.0

; JOY\_CLK = (0), clock

DELAY(1)

djnz

Count1, :Read_Joy_Bit_Loop

; reset all joystick control bits

W, RA

W, JOY_PORT_MASK

W,#(JOY_PORT_CLK_0 | JOY_PORT_SH_nLD_0)

mov

and

or

nop

mov

ret

```

You may notice the **DELAY** macro in the code, this is simply a macro that delays the sent number of clocks, for example **DELAY(10)** would delay 10 clock cycles. The implementation of **DELAY** is below for reference:

```

pelay Macro clocks

; first compute fractional remainder of 10 and delay

IF ((clocks // 10) > 0)

; first 3 clock chunks6

REPT ((clocks // 10)/3)

JMP $ + 1

ENDR

; now the remainder if any

REPT ((clocks // 10)//3)

NOP

ENDR

ENDIF

```

# WARNING!

If you find that the Read\_Joysticks function isn't working then slow it down by increasing the delays between states.

To use the Read Joysticks function, you might do something like this:

```

mov data8, #0; clear joystick return vars

mov data16, #0

call Read_Joysticks

```

And joystick 0 would be placed in data8 on return and joystick 1 in data16 on return respectively

### 11.6.4 Joystick Demo

To demonstrate reading the joysticks I have written a program that read both joysticks and then exports their values out to ports B and C, so you can view them with the mini-logic probe. We have to stoop to this level since there is no "printf()"! Anyway, load the demo program **JOY XME 01.SRC** located on the CD at:

```

CDROOT:\XGSME HW CD\XGSME Sources\jov xme 01.src

```

into the XGS Micro Edition Studio, Assemble it, and program it into the XGS ME unit. Remember, you must have the XGS ME power on and the SYSMODE switch at the rear must be in the **PGM** or Program mode to upload to the XGS ME. To run the program place the XGS in **RUN** mode and hit **RESET** and the program will run at the full 80Mhz.

When you run the program, to verify that things are working, you will plug you joysticks into the ports and then move them around. The demo will drive the ports as shown in Table 11.5.

Table 11.5 – Joystick demo program driver output.

| Joystick 0 |                 |          | Joysti | Joystick 1 |  |  |

|------------|-----------------|----------|--------|------------|--|--|

| Up         | <del>&gt;</del> | Port RB0 | Up     | → Port RC0 |  |  |

| Down       | →               | Port RB1 | Down   | → Port RC1 |  |  |

**Design Your Own Video Game Console**A Beginner's Guide to Video Game Console and Embedded System Design, Development, and Programming.

| Left  | → | Port RB2 | Left  | → Port RC2 |

|-------|---|----------|-------|------------|

| Right | → | Port RB3 | Right | → Port RC3 |

| FIRE  | → | Port RB4 | FIRE  | → Port RC4 |

If you wish you can probe these ports with a logic probe (connected to power and ground) and see them change as you move the joysticks around.

In this section we covered all there is to know about the XGS ME's joystick inputs. There is of course a lot more to the hardware as far as its abilities to interface to other serial devices, but the designs should give you all the insight you need into the extra bits in the shift registers and the serial expansion port (on the right side of the board).

## 11.7 Keyboard Interface and Programming

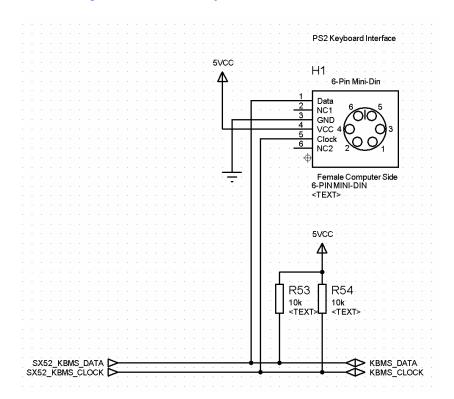

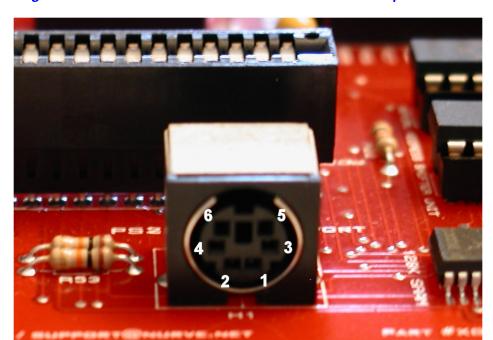

The PC keyboard and mouse both follow the exact same kind of protocol, so we are only going to discuss the keyboard since the mouse is very similar. Referring to Figure 11.11 for the keyboard hardware and the design file:

Figure 11.11 – The Keyboard Hardware Interface

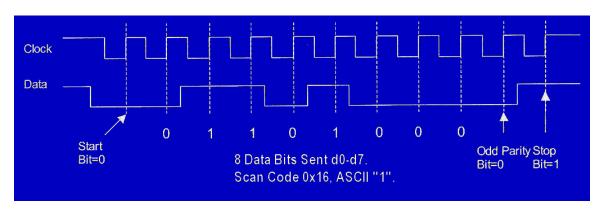

The keyboard protocol is straightforward and works as follows; for every key pressed there is a "scan code" referred to as the "make code" that is sent, additionally when every key released there is another scan code referred to as the "break code" that in most cases is composed of \$EO followed by the original make code scan value. However, many keys may have multiple make codes and break codes. Table 11.6(a) lists the scan codes for keyboards running in default mode.

Table 11.6(a) – Default Scan Codes.

| KEY | MAKE | BREAK | KEY          | MAKE                            | BREAK                     |  | KEY     | MAKE  | BREAK    |

|-----|------|-------|--------------|---------------------------------|---------------------------|--|---------|-------|----------|

| А   | 1C   | F0,1C | 9            | 46                              | F0,46                     |  | [       | 54    | FO,54    |

| В   | 32   | F0,32 | `            | 0E                              | F0,0E                     |  | INSERT  | E0,70 | E0,F0,70 |

| С   | 21   | F0,21 | _            | 4E                              | F0,4E                     |  | HOME    | E0,6C | E0,F0,6C |

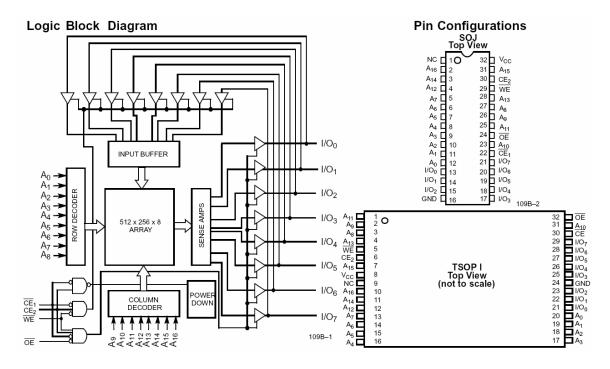

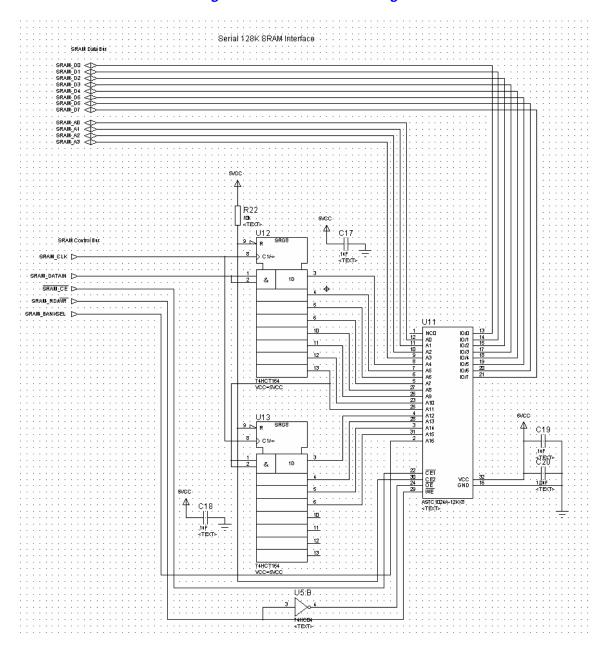

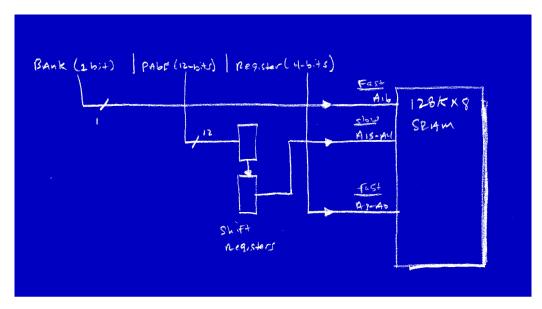

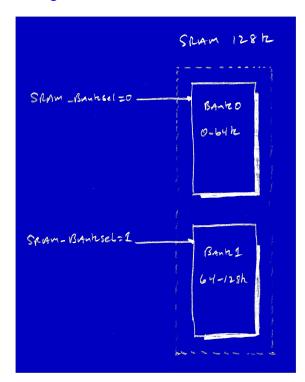

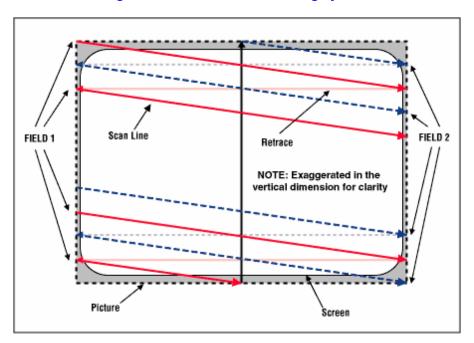

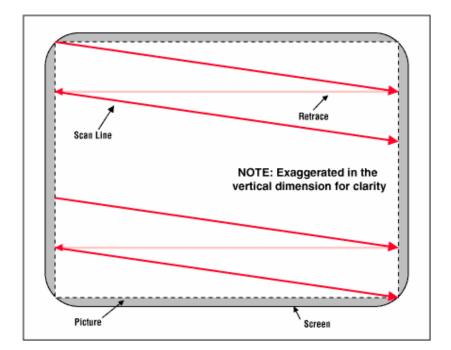

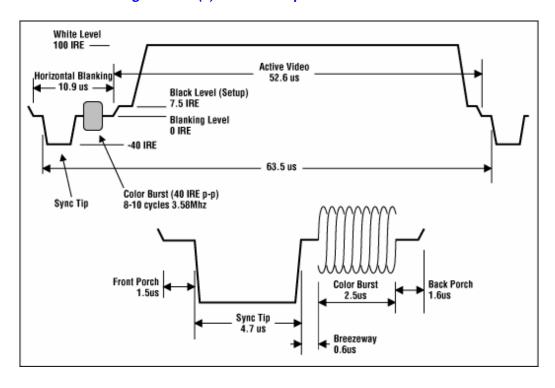

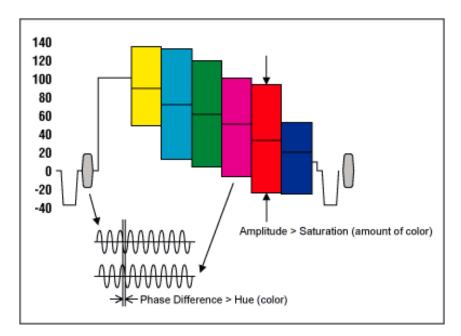

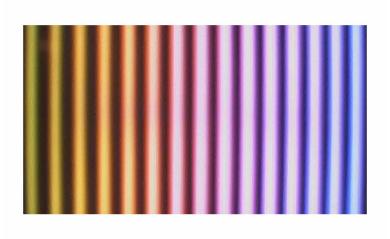

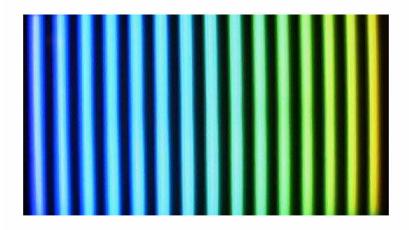

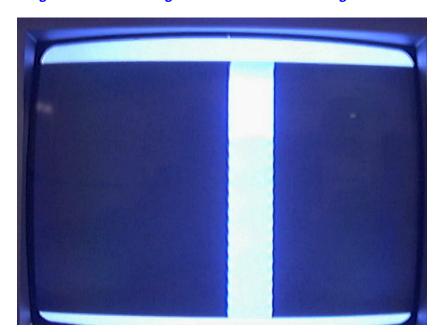

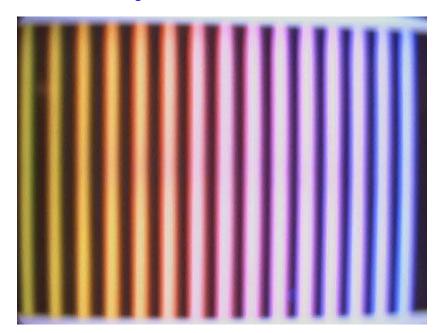

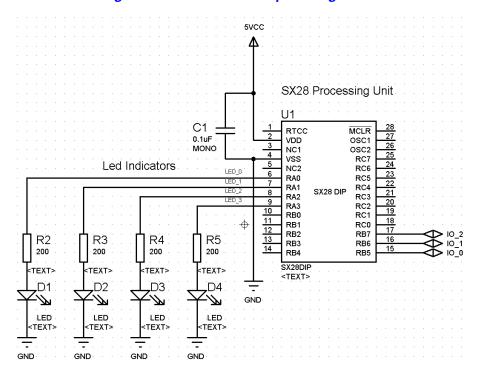

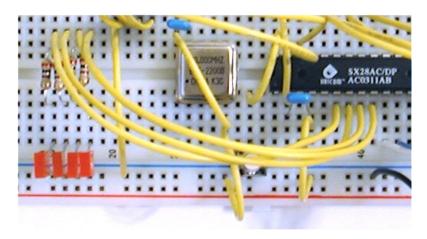

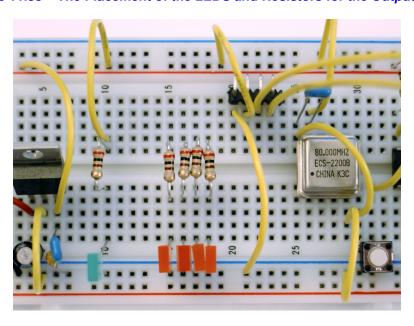

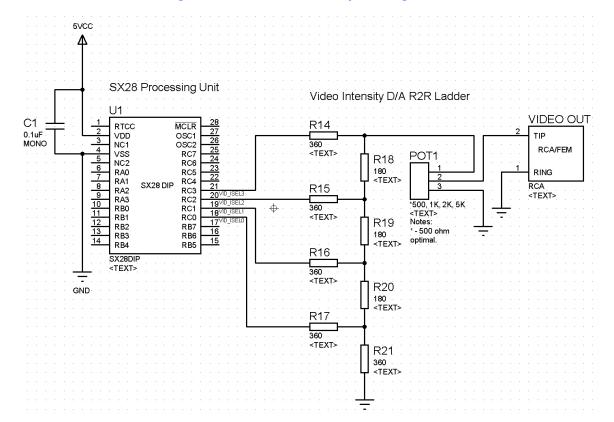

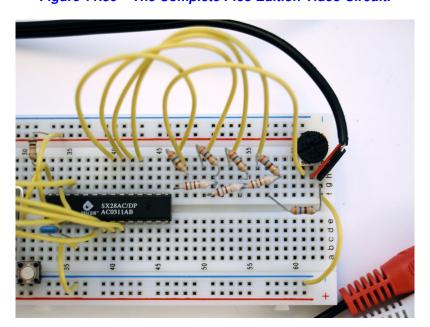

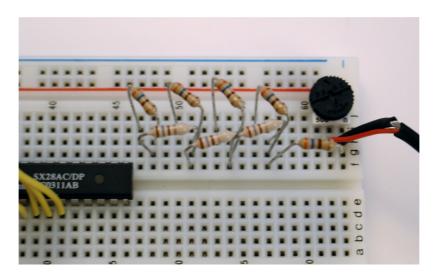

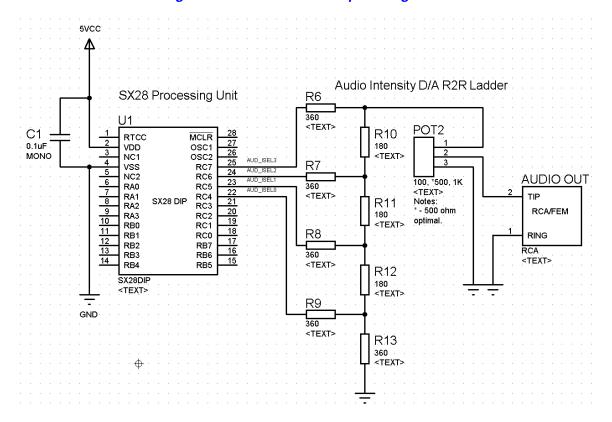

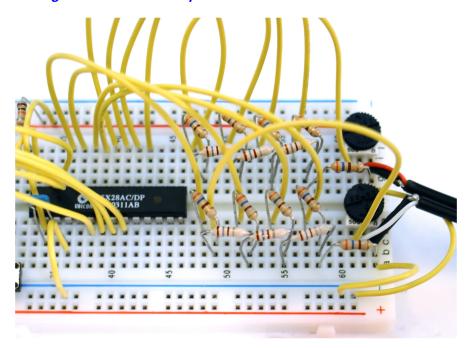

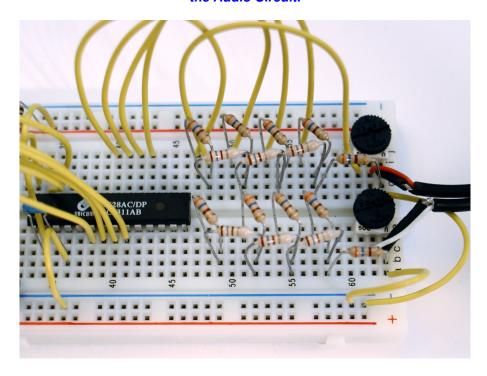

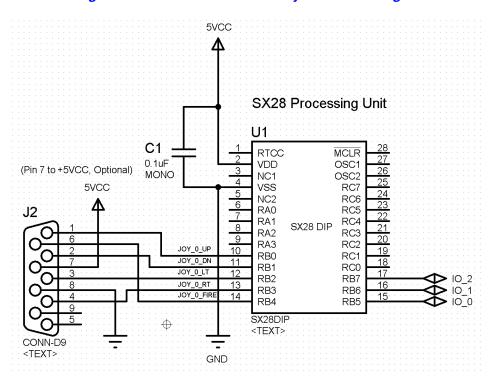

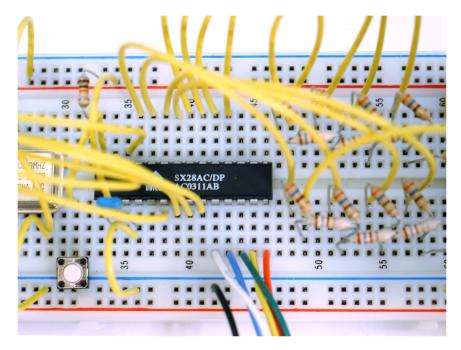

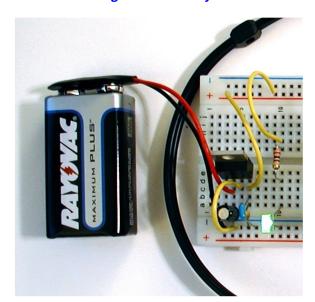

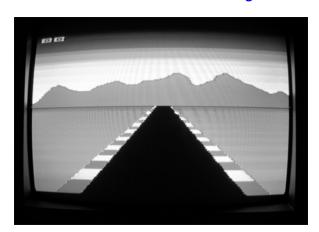

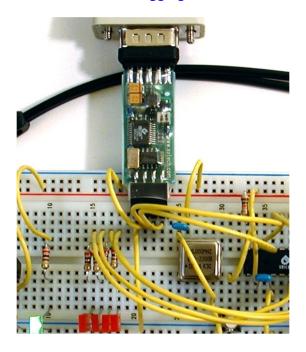

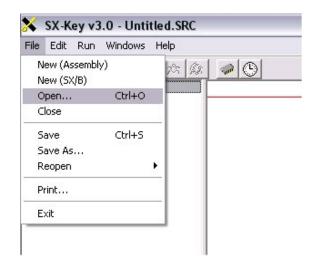

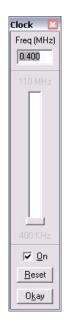

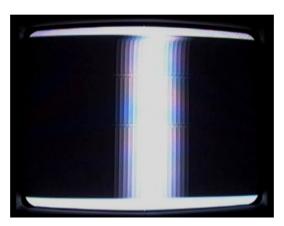

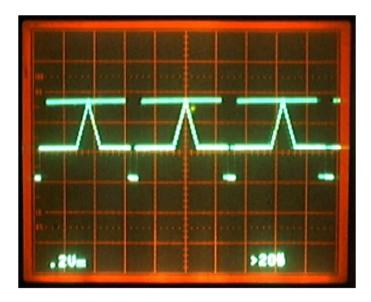

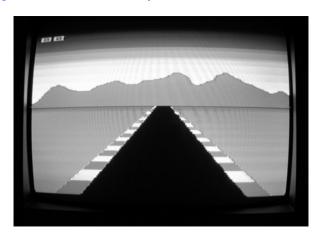

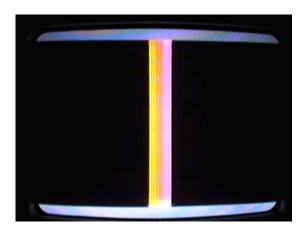

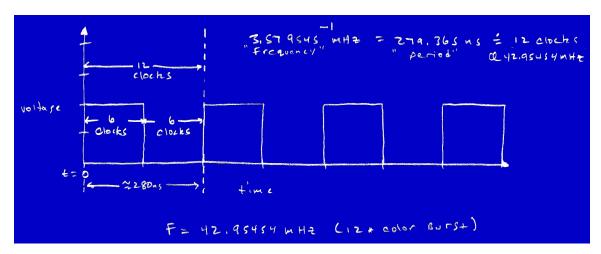

| D   | 23   | F0,23 | =            | 55                              | FO,55                     |  | PG UP   | E0,7D | E0,F0,7D |